# **FACULTY OF ELECTRONICS**

## **SECUNDERABAD**

## **CERTIFICATE**

Certified that this is a bonafide report of the dissertation work done by Major Ajay Malik during the year 1998 in partial fulfilment of the requirement for the award of the Degree of Master of Technology in Electrical Engineering by the Jawaharlal Nehru University, New Delhi.

Guide.

Dr. D P Roy,VSM RC Dept Faculty of Electronics MCEME

#### ACKNOWLBDGBMBNT

1. I consider it a pleasant duty to express my heartfelt gratitude, appreciation and indebtedness to Dr D P Roy, VSM for his able guidance for successful completion of this dissertation.

.

2. I am thankful to Dean Faculty, Brig Surinder Singh, Head CE Dept, Col G Ankaiah and the staff of Line Engg Gp for their kind pursuance, cooperation and providing necessary facilities for timely completion of the dissertation.

3. Co-operation extended by other staff of faculty directly or indirectly is also acknowledged.

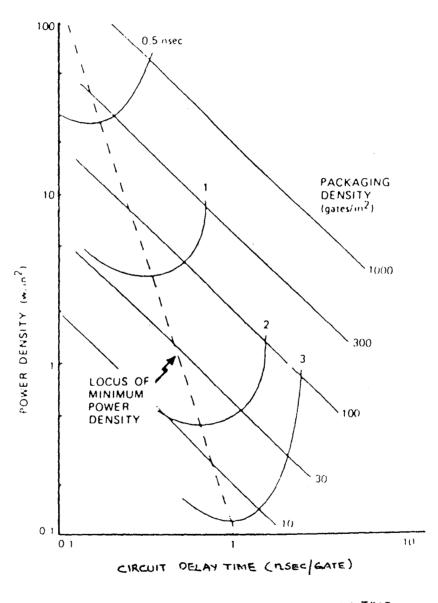

### CONTENTS

,

| <u>SNo</u> | Topic                                                             | Page No |  |

|------------|-------------------------------------------------------------------|---------|--|

| 1.         | Introduction                                                      | 1       |  |

| 2.         | Semiconductor Developments                                        | 5       |  |

| 3.         | Surface Mount Electrical Components                               | 26      |  |

| 4.         | Packaging and Interconnecting Structures                          | 31      |  |

| 5.         | Electrical Design Considerations                                  | 34      |  |

| 6.         | Thermal Management                                                | 40      |  |

| 7.         | Printed Board Design Considerations                               | 42      |  |

| 8.         | Multilayer Board Fabrication &<br>General Assembly Considerations | 46      |  |

| 9.         | Chip On Board Technology                                          | 56      |  |

| 10.        | Microminature Multichip Module                                    | 81      |  |

| 11.        | Conclusion                                                        | 97      |  |

| 12.        | 8 ib 7 iography                                                   |         |  |

#### INTRODUCTION

1. <u>Interconnection Systems</u>. Advances in interconnection systems have occured in response to the evolution of electronic technology, particularly the growth in component sophistication, complexity, and number of electronic circuit component terminals to be interconnected. But a basic concern has developed with the progress of interconnection technology. A variety of factors have contributed to this growing concern, among which are the following :-

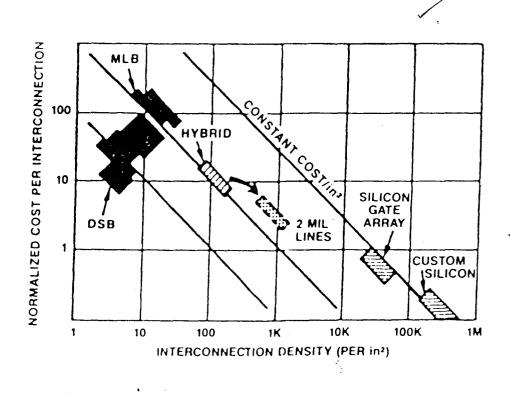

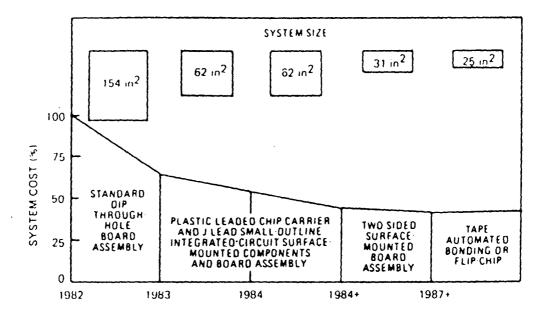

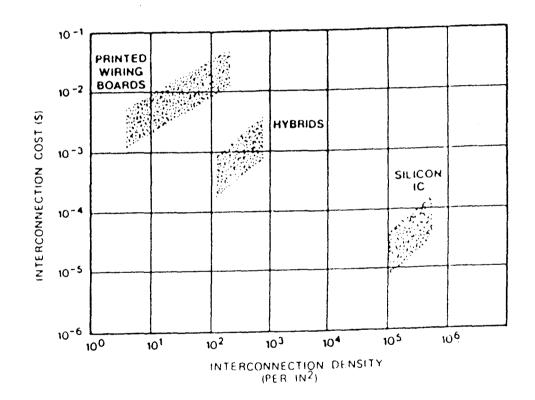

(a) <u>Interconnection Costs</u>. These have not followed the decline in device costs (Fig 1). Today a complete computer-on-a-chip costs less than the surrounding components and interconnection system.

(b) <u>Operating Speeds</u>. There is a strong trend towards increased use of the faster-operating integrated circuits (ICs). The interconnection system serving them should have configurations that make it possible to locate all such devices within a very limited area in order to avoid or minimize excessive propagation delays in the wiring.

(c) <u>Integration of Functions</u>. Further integration of circuit functions within dual-inline packages (DIPs) is becoming more limited, in part by the practical considerations of the economical size of the ICs and DIPs suitable for easy design change and field repair.

FIGURE -1

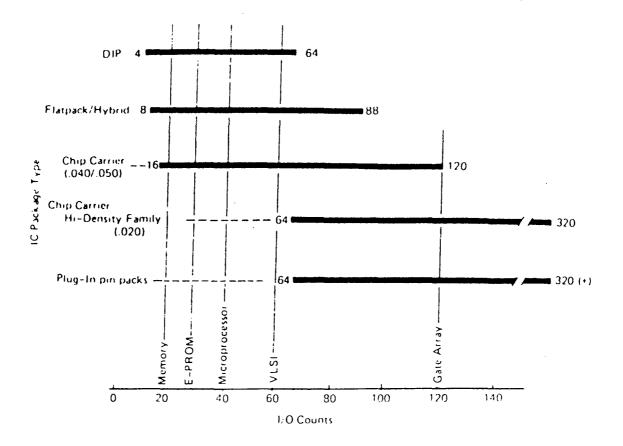

(d) Lead Spacing. Any increase in the number of leads per IC package calls for more interconnections between them (Table 1). Large-scale integrated circuits (LSIs) having 48 up to 150 leads cannot be efficiently packaged from in familiar DIP configuration with two rows of the leads on 0.1-inch centers. These devices will require the new packages that are coming onto the market.

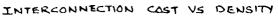

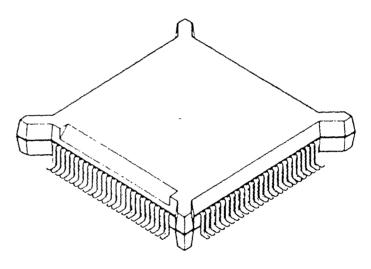

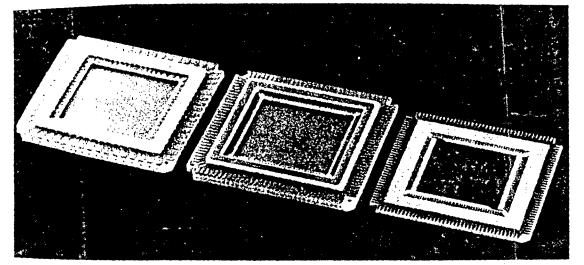

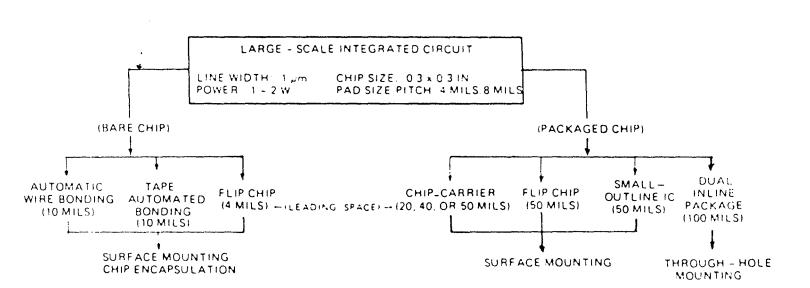

2. Semiconductor Device Technology. The application of the emerging higher-speed, higher-density ICs offers great potential for increasing the performance of complex electronic systems. This is especially true in applications where size, weight, and power requirements are critical. In order to fully utilize the potential of these new devices, compatible packaging technology new definition of the is required. This demands a interconnection system. The significance and magnitude of these new interconnection system requirements can be seen by appreciating the development of semiconductior technology (Fig 2).

3. As the semiconductors in electronic equipment go to the use of VLSI (Very Large Scale Integration), there will be a greater percentage of the total system cost, of the total design and manufacturing time, and of the lesting costs affected by the packaging/interconnection system technology. Also, chip packaging levels will increase to over 10,000 gates/chip and board pinouts will approach 300, with proportional increases in power to be dissipated per unit volume. The use of peripheral devices such as DIPs and chip carriers, or matrix devices, such

-2-

.

|      | Typical Packaging situation                | number of connecti-<br>pins per capacity | Required<br>connective |             |             |             |

|------|--------------------------------------------|------------------------------------------|------------------------|-------------|-------------|-------------|

| Case |                                            |                                          |                        | 50-mil grid | 25-mil grid | 20-mil grid |

| 1.   | 1-16 pin DIP per in. <sup>2</sup>          | 15                                       | 34                     | 2 (1.7)     | 1 (0.8)     | 1 (0.7)     |

| 2.   | 22-pin DIP on 1-in. centers                | 20                                       | 45                     | 2.3 (2.3)   | 1+ (1.13)   | 1 (0.9)     |

| 8.   | 2-16 pin DIPs per in. <sup>2</sup>         | 30                                       | 67                     | 3-4 (3.4)   | 2 (1.68)    | (1.34)      |

| 4.   | 40-pin DIP on 1-in. centers                | 20                                       | 45                     | 2-3 (2.3)   | 1+ (1.13)   | 1 (0.9)     |

|      | 24-pin chip carriers on<br>0.7 in. centers | 50                                       | 112                    | ~6 (5.6)    | ~3 (2.8)    | ~3 (2.2)    |

| •    | 24-pin chip carriers on<br>0.5-in. centers | 16                                       | 216                    | ~11 (10.8)  | ~6 (5.4)    | ~5 (4.3)    |

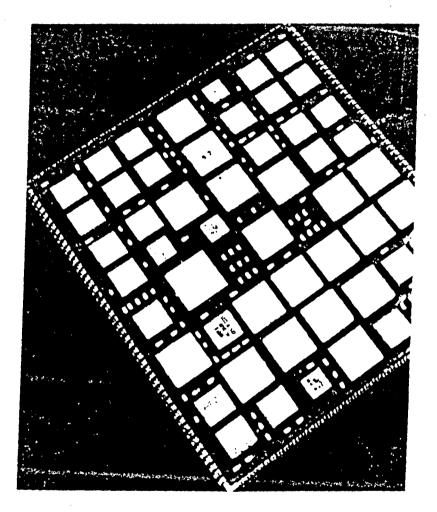

|      | Connective capa                            | city per leve                            | 1, in.∕in <sup>2</sup> | 20          | 40          | 50          |

Connectivity Capacity Requirements for Dual-Inline Packages (DIPs) and Small Chip Carriers (Dimensions Only in Inches)

SEMICONDUCTOR TECHNOLOGY DEVELOPMENT

FIGURE - 2

as pin-grid arrays, will significantly affect packaging density and therefore, the interconnection system.

4. <u>Surface Mounting</u>. Present component interconnection technology is based to a great extent on the use of platedthrough holes, and therefore all devices or their packages must have leads that will be eventually soldered into these holes. These component leads add to material costs, assembly labour, and manufacturing problems, but they are conceptually totally avoidable.

5. The newly emerging packages are radically resolving this problem, since they are designed for the surface mounting of planar components on a planar surface and do not require discrete component leads and plated-through holes for their termination. This development will have a profound impact on future interconnection methods, because the surface-attachment approach achieves the following :-

(a) Eliminates the cost and labour for component leads and their forming.

(b) Simplifies the problems of component shipping and handling by the elimination of their delicate leads.

(c) Simplifies assembly, since there are no leads to preform. Also, the self-centering capability of many of these new devices during the soldering operation makes them tolerant to some component placement misalignment. (d) Increases the component placement rate from 300 units/ hour (for manual assembly) or 3,000 or more units/hour (for automated methods) by one more order of magnitude, e.g., 200 units in 7 sec on an 8- by 10-in. board is achievable.

(e) Simplifies the soldering process by assembling with solder-reflow systems that use vapor-condensation methods without the need to worry about leads protruding on the underside of the substrate.

(f) Improves connectivity/unit area on the underlying substrate by reducing hole diameters, or by totally eliminating the need for holes.

6. <u>Summary</u>. Microelectronics has revolutionized the architecture and design concepts of the present day products. Every two or three years a new technology generation is announced. 1991 saw the breakthrough of a feature size of 0.8 micron for CMOS and 1992 saw that of 0.5 micron. Most developments are using three interconnection layers as a tripple layer metallization will be mandatory for 0.5 micron technologies because interconnection delays have become more significant than gate delays. It is therefore time that due consideration is given to surface mount and chip on board technologies for optimizing the chip space.

#### SEMICONDUCTOR DEVELOPMENTS

#### <u>General</u>

7. Much has been written about Surface Mount Technology (SMT) and how, in general terms, it better satisfies the growing demand for packaging and interconnecting high-technology integrated ccts, than does conventional through-hole technology. However, now that an SMT state-of-art is beginning to emerge, this is an appropriate time to become more specific about the new developments in semiconductor technology that are driving force behind SMT and, thereby, behind printed board technology.

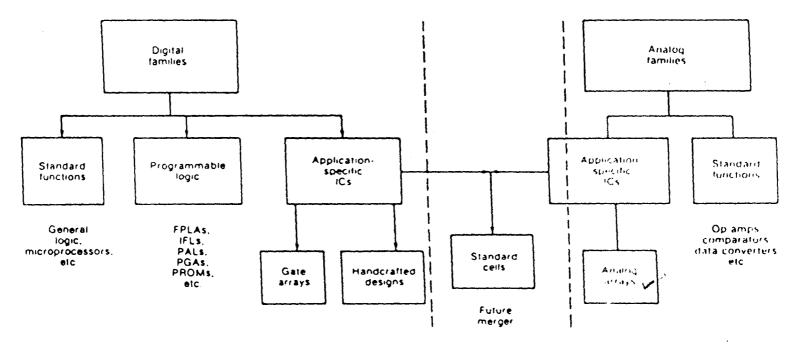

8. During the last few years, the number of approaches available to cct designers to use (or create) integrated ccts has blossomed into a wide variety (Table 2). Therefore, an endeavour is made to first describes the standard semiconductor logic and the sophisticated custom/semicustom ways in which they are being combined by integrated cct (IC) manufacturers and this is followed by a discussion of how this impacts end-product applications. Finally, their ultimate impact on surface mountrelated issues is covered.

9. <u>Integrated Circuit Logic Families</u>. A cct designer can work with one of several integrated cct transistor structures. The two most popular are bipolar and metal oxide (MOS) silicon chip technologies. These, in turn, are beginning to receive competition from the newly emerging gallium arsenide (GaAs) chip structures.

-5-

## TABLE 2 /

|                                                       | GaAs                                                               | ECL                                                                         | CMOS                                            |

|-------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------|

|                                                       | ning digh thin and four hand over one over line and have twee love | anar maa anar may ang ang biyi jibu kuta kuta ting ting ang ang ang ang ang | ne alle mid ben hee foe det det den son det son |

| Critical dimensions (Micro meter) 🗸                   | 1.0                                                                | 2.0                                                                         | 2.0                                             |

| Chip size (mm <sup>2</sup> )                          | 4.6 x 4.3                                                          | 6.6 x 6.8                                                                   | 10 x 10                                         |

| No of equivalent gates                                | 1200                                                               | 2500                                                                        | 20K                                             |

| Time delay (psec/gate)                                | 375                                                                | 510                                                                         | 1500                                            |

| Power dissipation (Micro Watt/gate)<br>(50-MHz clock) | 190                                                                | 1200                                                                        | 310                                             |

| Speed-Power (f )                                      | 71                                                                 | 610                                                                         | 465                                             |

•

## Examples of High Speed Integrated Circuits [7]

10. The demise of the standard silicon-based logic families has been forecast for almost as long as standard logic has been around. And true, the standard logic families that exist today are a far cry from those of the 1960s. Yet their use persists. Simple one- and two-gate chips are gradually being made obsolete by standard medium-scale integration (MSI) and in some cases, by large-scale integration (LSI) chips with larger functions. However, the most basic building block functions will remain as extra "glue" circuits for many years to come.

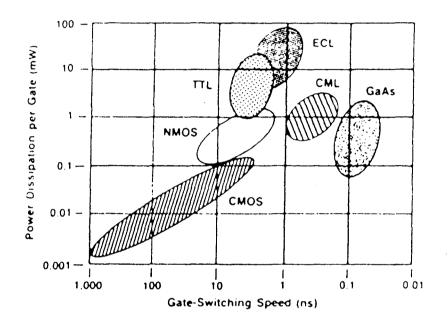

11. Gate-switching speed, power dissipation, and functional density are the basic differences separating the integrated circuit technologies at the low-integration levels (Fig 3). However, these are no longer valid in the very-large-scale integration (VLSI) era. Thus, the answers to selection questions lie in understanding the available technologies from the new perspective of identifying the applications areas most generally suited for each technology and the key system design trade-offs involved in the use of each technology.

12. <u>Bipolar Circuit Technolgy</u>. Bipolar transistors can be formed by either alloy or double-diffused techniques. However, all major bipolar "integrated" ccts use double-diffused transistors formed in an epitaxial (high-resistivity film) layer deposited on the silicon wafer. The epitaxial layer serves as the "collector" region of the transistor and allows for easy isolation of the separate cct components with the addition of a deep diffused "fence". Because they are formed below the wafer surface, bipolar

-6-

•

WIDE VARIETY OF INTEGRATED CIRCUIT TECHNOLOGIES

Semiconductor Developments

•

٠

transistor are not prone to contamination. Unsensitivity to contamination is not the only factor, however, they can operate at voltage and current values that are compatible with other electrical devices. The switching speeds of bipolar transistors are also faster than those of the simpler MOS discrete transistors.

13. Using conventional bipolar structures, cct speed can be improved by "wiring" together the various elements into logic cells. Transistor-transistor logic (TTL) and emitter-coupled logic (ECL) are the two most popular cell types.

14. TTL ccts have been popular with most system builders because of a combination of acceptable performance and ease of design. Alternately, ECL design has been a standard process only for computer builders who need high performance badly enough to put up with the special headaches by the use of the higher-speed ECL ccts. For example, printed board conductors must be designed with wave guide (controlled impedance) techniques because the rise time of ECL signals puts them in the microwave freq range. This point will be discussed in greater details subsequently.

15. <u>MOS Circuit Technology</u>. The formation of MOS integrated cct devices is different from bipolar technology. The basic MOS fabrication process starts with an incoming wafer that is processed through oxidation and goes directly to masking. Thus, it can eliminate the epitaxial layer and isolation diffusion steps reqd in bipolar technology. The absence of the isolation structure allows a higher MOS component density than bipolar technology.

16. In both bipolar and MOS technology, the area of the cct that does not contain active devices is called the "field". A particular problem arises over the field in MOS ccts. Metal conductors running on top of the field oxide form a capacitor with the silicon below. If the voltage on the conductors becomes high enough, the "field capacitor " will create charge in the underlying silicon and cause shorted devices. Additional wafer processing is read to overcome this problem. (More careful handling during the printed board assembly processs is also read).

17. Unlike the simpler metal gate processing, complementary MOS (CMOS) requires more processing steps than the biploar process. However, this additional processing results in CMOS devices that have lower power comsumption and increased speed, making them attractive for many applications.

18. The Departments of Defence of all the countries and the aerospace industry have stepped up their requirements for increasingly higher tolerances against radiation effects for integrated ccts. These stricter mandates are expected to yield system survivability in hostile (nuclear) environments. greater technology is inherently more radiation-resistant Bipolar than most CMOS processes. Thus, the advantages of designing with CMOS have led to additional processing steps to enhance CMOS survivability. Other CMOS processing variations prevail to

-8-

customize particular features of the end product. This, in many cases, makes CMOS the most complicated and most involved technology in the industry.

Gallium Arsenide Technology. Gallium arsenide (GaAs) 19. is an ideal semiconductor medium for achieving very high speed in electronic devices and integrated ccts. This is because its energy band structure is such that electrons in GaAs are exceedingly "light" and highly mobile. Thus, electron velocities measured in GaAs transistor structures range upto about five times those achieved in silicon-based devices.

20. Further more, GaAs is readily available in a semi-insulating substrate form that substantially reduces parasitic capacitances, so that its outstanding device speeds can be fully realized in integrated ccts (Fig 4). This high speed, plus power dissipation that often tends to be substantially lower than that of highspeed silicon devices, accounts for the growing interest in gallium arsenide.

21. Although a number of different GaAs integrated circuit families exist, it is possible to draw some general conclusions about the advantages of GaAs technology over silicon technology.

22. Currently, for the same power consumption, GaAs is about half an order of magnitude faster than emitter-coupled logic (ECL), the fastest silicon-based family.

(a) GaAs is more radiation-hard than silicon. At this time, however, the difference is difficult to quantify.

SPEED VS POWER COMPARISONS FOR VARIOUS TECHNOLOGIES.

FIGURE-4

(b) GaAs is better suited to the efficient integration of electronic and optic components. The usefulness of GaAs for this type of integration is still under investigation. However, if developed to the appropriate level, this may have a major impact on system design in general.

23. Basic disadvantages of GaAs technology, as compared to silicon technology, are as follows :--

(a) GaAs wafers presently exhibit a large "density of dislocations". That is to say, there are a large number of irregularities per unit area. Consequently, GaAs chips have (military writing) :-

(i) To be smaller in area.

(ii) A smaller transistor count.

(iii) A poorer yield. Of course, chip size can be traded off against production yield to some extent.

(b) GaAs substrates are about two times more expensive than silicon substrates. Moreover, GaAs is brittle Wafers can be damaged easily during the fabrication of intergrated circuits.

(c) The noise margin of GaAs at present is not as good as that of silicon. Thus, it is often necessary to trade off chip area for higher reliability.

(d) Lastly, some companies are currently reporting problems with the testing of designs for high-speed GaAs integrated

circuits. Testing facilities that are fast enough are simply not yet available. But this situation is expected to improve.

Application Specific Integrated Circuits. Electronic system 24. design is becoming more complex, with architectures reaching new heights of sophistication and expanding integrated circuit choices. Yesterday's systems comprised off-the-shelf, smallscale (SSI) and medium-scale (MSI) levels of circuit integration. However, many of today's designs are implemented with customized large-scale (LSI) and very-large-scale (VLSI) integration. Leading the migration toward LSI/VLSI are applicaion-specific integrated circuits (ASICs) with functions tailored to the user's requirements.

25. Therefore, in order to keep their competitive edge, system manufacturers must make informed decisions when slecting a particular type of customized integrated circuit technology. This often requires an in-depth trade-off analysis.

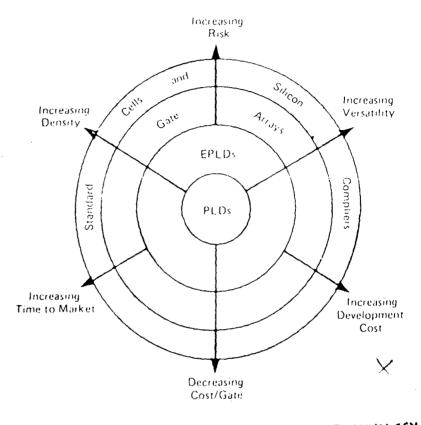

26. There are four general ASIC categories :-

(a) Programmable Logic Devices (PLDs).

(b) Gate/macrocell arrays.

(c) Cell-based devices (both standard/macrosystem cells and silicon-compiled cells).

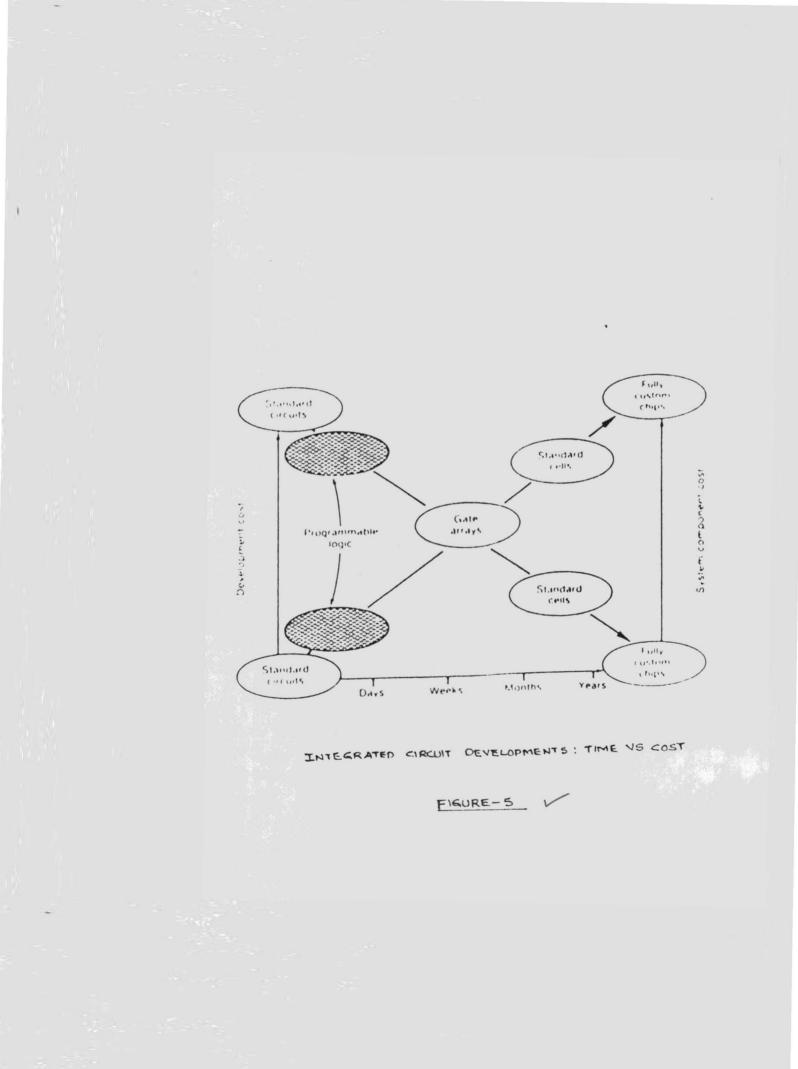

(d) Handcrafted, fully custom integrated circuits (Fig 5). The gate arrays and cell-based devices are often called semicustom integrated circuits. Also, recent advances in

#### ASIC Technology Selection Factors

|                                                                | ASIC types             |                              |                                  |                                       |  |

|----------------------------------------------------------------|------------------------|------------------------------|----------------------------------|---------------------------------------|--|

|                                                                | Programmable,<br>logic | Gate/macroce11               |                                  |                                       |  |

| Chip density (number<br>of gates)                              | Few                    | 16-100,000                   | Hundreds to tens<br>of thousands | From hundreds to<br>tens of thousands |  |

| Percent of wafer pre-                                          | 100                    | 80-90                        | 0                                | 0                                     |  |

| Time to prototypes<br>(weeks, in 1983)                         | Off-the-Shelf          | 7-13                         | 13-26                            | 39-104                                |  |

| Option development cost<br>per chip (depends on<br>complexity) | None                   | \$10,000-\$40,000            | \$40,000-\$100,000               | \$100,000-\$500,000                   |  |

| Ability to make design<br>changes or correction                | Minimal cost           | Easy, fast, and<br>expensive |                                  |                                       |  |

| Unit production cost                                           | Low                    | High                         | Medium                           | Lowest                                |  |

ASRC - Application Specific PC.

0

integrated circuit fabrication are spawning a new kind of ASIC between a PLD and a gate array. It is important to determine which type is best suited to a designer's requirements (Table 3). The first consideration is the density of the device needed. For example, PLDs have relatively low densities of from 50 to 5000 equivalent gates per chip.

27. Macrocell and gate arrays are next, with densities ranging from 500 to 10,000 gates per chip, sometimes more for specific purposes. Standard cells have still higher densities, many thousands of equivalent gates per chip. Hand-packed custom circuits are the densest, with 70,000 switching transistors per chip being not uncommon.

28. The time to prototype and develop an ASIC is best suited for an application. Because PLDs are readily available off the shelf, prototypes can be obtained almost immediately at a relatively negligible development cost. Gate array and macrocell array prototypes development time is typically from 7 to 13 weeks, with prototype costs from \$10,000 to \$40,000. Standard cells take even longer, typically from 13 to 26 weeks, because their wafers are made from scratch instead of being preprocessed like macrocell and gate array chip.

29. Additionally, standard-cell prototyping costs are usually between \$40,000 and \$100,000. Handpacked, fully custom chips have the longest prototyping times, taking from 39 weeks to 2 years, with costs ranging from \$100,000 to more than \$50,000.

-12-

30. FLDs are often the logical choice when the product i.s required immediately or when frequent design changes are tο They are limited, though, to relatively simple occur. requirements when compared to the functionality and densities of the other ASIC technologies. Its functional and volume requirements are high, gate array and macrocell solutions are usually the most feasible, with standard cell circuits the choice for the highest-volume demands. However, the better silicon usage characteristics of standard cells may offset their higher development costs if the volumes are suitable.

31. Silicon-compiled ASICs, though still in their infancy, also deserve consideration. Handpacked, oustom circuits are often acceptable when the largest production quantities are needed and if the long turnaround time can be tolerated by the user.

32. <u>Programmable Logic Devices</u>. Until recently, programmable logic devices (PLDs) were considered for use primarily as TTL "glue" replacements in order to compact several gates into a single package when there were shortages in printed board space. They were not really accepted as a valid ASIC choice. But that has changed, due to four basic reasons :-

(a) The first is the trend toward acceptance of PLDs as a mainstream system building block, such that the designer begins a design with PLDs in mind, as opposed to their being an afterthought.

-13-

(b) The second reason is the sudden proliferation of PLD manufacturing technologies. Just as digital logic gates began with bipolar chips, so did PLDs. Now, however, PLDs are available in a selection that also includes CMOS and ECL technologies.

(c) Third is the growth in the complexity and functionality of PLDs. Early PLDs (in-20-pin, dual-inline packages, DIPs) had usable gate comunts in the 100- to 300-gate range. Now, gate densities have climbed to as high as a few thousand. (Pin counts, have also increased to as high as 84). The result is that such devices now offer logic densities that once were the exclusive domain of gate arrays and cell-based parts.

(d) The fourth reason is the increase of PLD manufacturers, from three in 1079 to more than 20 today. This has served both to increase the selection of functions available to the designer and to make the cost of the devices more competitive.

Applying CMOS and erasable-cell technologies to the basic D configuration has created crasable programmable logic devices PLDs) with a new level of versatility in logic design. In rtain applications they match the density of gate arrays thout the associated tooling costs, extended development hedules, and loss of in-house design control. Thus, EPLDs fit tween PLDs and gate arrays in terms of complexity, versatility, d cost per function (Fig 6).

- 14-

.

TRADE OFFS KIHILE SPECIFYING ASIC TECHNOLOGY

FIGURE -6

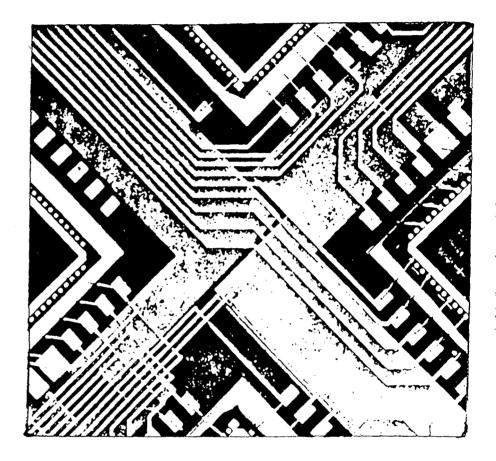

34. <u>Gate Arrays.</u> Gate arrays are distinguished by their use of prefabricated chips containing transistors and "feedthroughs," none of which are interconnected by signal wiring (Fig 7). As a result, the chip vendor can make large quantities of identical unwired gate array chips, fabricating the wiring only when a customer supplies the circuit schematics or interconnect lists.

35. Since the fabrication of wiring layers is a relatively lowrisk, in-expensive operation, manufacturing yields tend to be high and processing times short. More important, design costs are low, since a manual layout phase is not needed.

36. Instead, design automation tools, which assign transistors and feedthroughs to circuit functions and determine the wiring paths, perform the layout task. The use of these tools is straightforward, consumes a relatively small amount of computational resources, and tends to produce final chips that are efficient in space and speed.

1

37. Arrays are available in all of, and combinations of, the basic integrated circuit fabrication technoligies. The mainstay of the fastest digital systems, silicon ECL gate arrays, face competition from the other technologies as new processes and materials become available. However, the same technological advances that give MOS its advantages will help bipolar arrays remain ahead of MOS as well as mixed bipolar-MOS and in stride with the subnanosecond speeds of gallium arsenide. In fact, ECL gate arrays will soon be available with as many as 10,000 gates along with gate delays of only 200 to 300 psec.

-15-

| 1 12 1 12 1 12 12 12 12 12 12 12 12 12 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| () d' faralaralle l'arrivale l'arrivale l'arrivale l'arrivale l'arrivale l'arrivale de l' |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| المتعادية المستحد المستح                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

ļ

BIPOLAR 28 ARRAY INTEGRATED CIRCUIT (GATE ARRAY)

FIGURE - 7

38. Nonetheless, ECL does stand to lose its edge in certain For instance, printed boards built previously with SSI fields. MSI ECL chips can now be replaced by high-density CMOS gate and arrays and mixed bipolar-CMOS chips with delys of several hundred picseconds and integration levels of 20,000 gates and higher. At the same time, GaAs may outrun ECL in some designs calling for extremely high speed. GaAs logic arrays and standard cells now have delays of only 200 psec or less with complexities up to a few thousand gates (Table 4).

39. <u>Cell-Based Technology</u>. Cell-based ASIOs can be implemented either as standard cells or as compiled cells. Both technologies provide high levels of integration, flexibility, and performance. The trade-offs are in degree of user involvement and functional capability.

40. Turnaround time and nonrecurring engineering costs are similar for the two approaches. However, designing with standard cells relinquishes more of the design effort to the device vendor than does the compiled-cell approach, which allows the customer to be more involved. Also, although the performance of standard and compiled cells may be the same at the transistor level, performance and density differences emerge at the chip level (Table 5).

41. It should be noted, however, that neither approach is inherently superior or preferable to the other. Rather, the decision to use one or the other depends on the application or parts of the application. For example, some on-chip memory is

-16-

| Typical State-of-the Art Gate Arrays |

|--------------------------------------|

|--------------------------------------|

|                      | Number of<br>gates | Gate<br>de lays | Package Pins   | Number<br>I/Os |

|----------------------|--------------------|-----------------|----------------|----------------|

| Bipolar gate array . | 8,000              | 210 psec        | 235 PGA        | 188            |

| CMOS gate array      | 20,000             | 400 psec        | 284 TAB or PGA | 238            |

| GaAs gate array      | 2,000              | 230 psec        | 88 LCC         | 80             |

|                                                | Cell<br>Compiler | Standard<br>Cell | Gate array           |

|------------------------------------------------|------------------|------------------|----------------------|

| Core size                                      | 1085 x 1112      | 1872 x 1740      | 2160 x 2112          |

| Number of transistors in core                  | 980              | 1286             | 1286                 |

| Transistor density (sq.mils per<br>transistor) | 1.91             | 3.93             | 5.49                 |

| Design time                                    | 4 days           | 7 days           | 7 days               |

| Performance (critical path<br>delay per gate)  | 45 nsec          | 68 nsec          | 49 nsec <sup>a</sup> |

.

#### Three Implementations of the Same Circuit

a - The gate array design is implemented in a faster CMOS process technology.

more easily implemented using comilers, while many logic functions are better implemented in standard cells. A few vendors even provide the ability to implement both approaches on the same chip for optimum flexibility.

42. A Standard cell uses a library of simple, fixed cells and soft macrocells (predefined combinations of cells). User involvement typically includes logic partitioning, schematic entry, simulation, and net list verification. Fixed-height cells are then arranged by automatic placement and routing programs in fixed-height rows separated by variable-width routing channels.

43. Standard cell placement and routing is usually handled by the device vendor rather than by the customer. After the place-and-route operation, the design is resimulated using actual wiring delay figures to help ensure accurate performance estimation.

44. A cell compiler is a design tool for automatically generating the layout, simulation models, and schematic symbols targeted for a specific function. However, since one compiler cannot generate layouts for all functions, a design environment usually includes a libarary of cell compilers or parameter-based software modules.

45. In concept, a system engineer can design a chip by identifying compiler functions that correspond to the block diagram description of a circuit. These functions are compiled by the software. The design process then proceeds in a manner that is similar to that for standard cells.

-17-

46. Fully Customised (Handcrafted) Devices. A fully customised device imples that little or no formality is exploited in easing the task of chip design. For VLSI circuits, custom design uses heirarchical design methods whereby the bottom-most design element or cell contains the basic circuits, much like cells in standard cell devices. The primary difference is that there is little or no predefined structure to a custom-designed cell.

47. These cells are then interconnected to form larger cells, which are interconnected to form still larger cells, and so on until the entire chip is completed. The cells are not constrained into predetermined rows but can be located anywhere on the chip to minimize wasted space. A typical custom-designed chip is shown in Fig 7.

48. Cell placement and net routing in a custom layout are complex tasks, especially if maximum cell packing is desired. Because regular channels for wiring are usually not created, the task of routing is less constrained than in channel routing.

49. Even in a custom layout, however, routing can be done in two steps. The first step, as in gate array and standard cell designs, is to assign nets to particular regions of the chip or channels, if all cells are rectilinerar. Then each region is routed by assigned routes to tracks.

50. Cell placement on a custom chip is similar to the procedure standard cell chips. in the standard cell for Again, as approach, the object is to minimize wiring length and

-18-

congestion, assuring 100% wireability, and to minimize the area used by cells on the chip.

51. Custom design and layout, the most time-consuming of the ASIC styles discussed in this chapter, produce the most area-efficient chips and usually the fastest circuits. The trade-offs are with respect to design time, performance, chip size, production yield, and costs (both component and system).

52. Specialised Technology. In addition to the state-of-theintegrated circuit technologies and architectures art just described, other, more specialized approaches are being undertaken to obtain more cost-effective performance than is presently possible. Efforts in these areas are either vendordriven (wafer-scale integration, silicon-on-sapphire, bubble memories, etc.) or user-driven (e.g., very-high-speed integrated circuits). Although in their relative infancy, developments in these technologies have a potentially great impact on printed board technology.

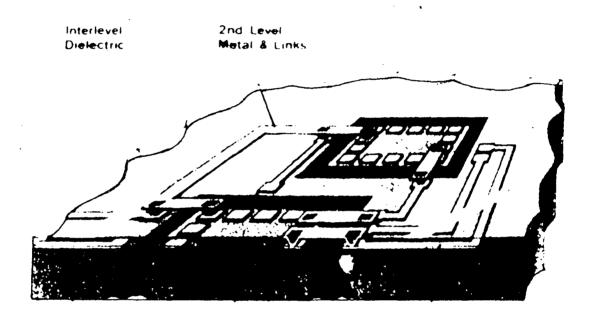

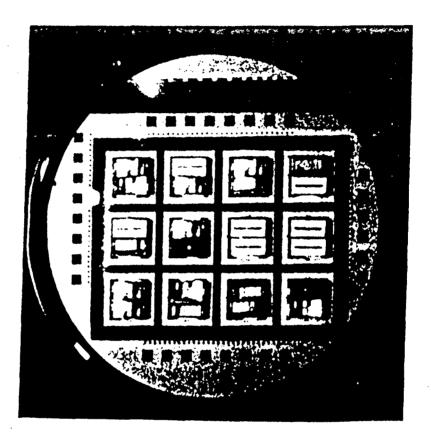

53. <u>Wafer-Scale Integration</u>. Wafer-scale integration (WSI) is conceptually the ability to interconnect electrically sound circuits on a tested and mapped semiconductior wafer using a wafer-level interconnect scheme. If achieved, WSI could open a market with almost limitless application. After nearly two decades of effort by several companies, however, a number of problems still exist (particularly in the wiring approach) that make these devices irrepairable, expensive, and, in general, unsuited to volume production. But because the benefits of WSI are so alluring, new companies (and approaches) have emerged to address the issues associated with this challenging integration concept.

54. Attempts so far to implement wafer-scale parts have concentrated on integrating highly complex devices with a random point-to-point wafer-level interconnect. Although integrating such devices will eventually result in wafer-level products with performance characteristics equivalent to a mainframe computer, testing the viability of such complex devices may be overly optimistic for such an immature technology. Integrating less complex, higher-yield circuits in a more structured or busoriented architecture might be a more realistic endeavour.

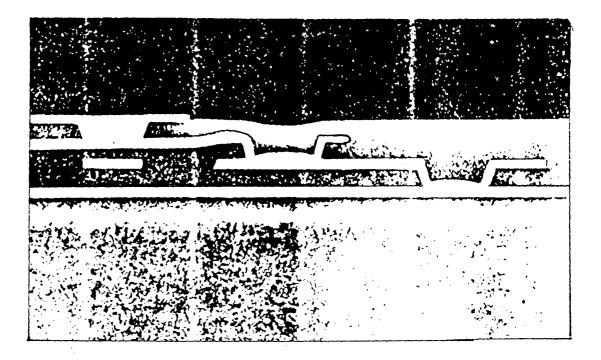

55. Memory devices are the most logical and likely candidates to usher in this new generation of WSI system designs. For one memory devices, in general are bus-oriented. This thing. makes routing less complex and less prone to error. Also, memory circuits are often constructed with a single layer of metallization, allowing the multichip macrocircuits to be interconnected with a second layer (this type of double-layer metallization is a commonly used fabrication technology). One of the most likely candidates for a WSI memory device is in airborne- or satellite-based electronics that would benefit from the decreased size and weight that WSI memory devices could provide along with reduced power supply costs, lower cooling costs, and improved space optimization.

-20-

Conversely, there are studies that indicate that WSI is 56. not for most applications. For example, there are those practical who feel that existing advanced VLSI-hybrid packaging approaches achieve circuit density, performace, and cost-effectiveness can levels comparable to those that WSI potentially possesses (Table 6). is also claimed that, in terms of packaging density, Tt thin-film multilayer hybrid circuits on varius substrates, when populated on both sides, can package almost 25% to 30% more components in about the same area as a wafer-scale device. The two technologies are almost equal as far as package delay concerned. (Double-sided thin-film hybrids rate 10.5-nsec versus 11.8-nsec for WSI when both have 450 output buffers per package).

57. In terms of power per chip, both single- and double-sided multilayer hybrid approaches are competitive with WSI. When the product of power times delay (an accepted figure-of-merit used to compare such technologies) is considered, double-sided thin-film hybrid circuits rate better than wafer-scale integration.

58. This is not to say that wafer-scale logic devices are not On the contrary, if worth developing. and when wafer-scale technologies have been fine-tuned, logic and system-level WSI might find a niche for it-self. When that time comes, however, comparable advances may have been made to improve the capabilities of the competing technologies. With respect to printed board technology, it does not appear that WSI will have serious impact within the near future. As Table 6 any shows. hybrid technologies are, and will continure to be, of more concern.

771- 7154

-21-

## TABLE 6

| Package                                                                         | Power<br>Versus<br>delay<br>(normal-<br>ized) | Ŭ    | Cost<br>(normal-<br>ized) | Overall<br>figure-of-<br>merit |

|---------------------------------------------------------------------------------|-----------------------------------------------|------|---------------------------|--------------------------------|

| Printed circuit board                                                           | 1.00                                          | 1.00 | 1.00                      | 1.00                           |

| Thick-film multilayer on ceramic                                                | 1.08                                          | 0.42 | 1.02                      | 0.46                           |

| Ceramic multilayer hybrid                                                       | 0.34                                          | 0.20 | 0.65                      | 0.044                          |

| Thin-film multilayer hybrid on<br>various substrates, populated on<br>one side  | 0.19                                          | 0.14 | 0.60                      | 0.016                          |

| Wafer-scale integration                                                         | 0.01                                          | 0.09 | 0.46                      | 0.0041                         |

| Thin-film multilayer hybrid on<br>various substrates, populated on<br>both side | 0.08                                          | 0.07 | 0.44                      | 0.0025                         |

1

### Figures-of-Merit for WSI Versus Typical Packaging Technologies (100-MHz Clock Rate)

Source : General Electric Corp.

.

59. <u>Silicon-on-Sapphire Devices</u>. In a silicon-on-sapphire (SOS) circuit, an isolating monolithic sapphire substrate is used as the circuit carrier. A thin silicon epitaxial film is grown on the sapphire surface, and transistors are then fabricated in the film by means of conventional CMOS technology.

60. Complete isolation is achieved between each device on the chip as a result of the use of the sapphire substrate. By virtue of this di-electric isolation, SOS is inherently immune to the destructive, high-current condition known as "latch-up." (Conventional CMOS must be processed with a special epitaxial layer to prevent latch-up.) This also helps to account for its exceptional resistance to transient radiation and "single-event upset" faults, which have been known to cause faults in integrated circuit memory cells.

61. The sapphire substrate also results in very low parasitic capacitances. This, in turn, results in higher circuit speed and lower power dissipation than is possible with bulk silicon MOS devices. Other comparisons between SOS and bulk silicon are shown in Table 7.

62. Unfortunately, the use of SOS has not been price-competitive in the marketplace because of higher manufacturing costs (wafer material, photomask replacement and dicing), lower demand, and fewer companies producing sapphire wafers. This will perhaps change when more semiconductor manufacturers adopt the technical advantages of SOS.

-22-

| TABLE 7                                 |      |

|-----------------------------------------|------|

| Silicon-on-Sapphire Versus Bulk Silicon | CMOS |

| Parameter                    | SOS    | Bulk   | 4 am |

|------------------------------|--------|--------|------|

| Design flexibility           | Higher | Lower  |      |

| Speed                        | Higher | Lower  |      |

| Power dessipation            | Lower  | Higher |      |

| Flicker noise                | Higher | Lower  |      |

| Leakage Current              | Higher | Lower  |      |

| High-temperature performance | Better | Worse  |      |

| Latch-up                     | . No   | Yes    |      |

| Radiation tolerance          | Higher | Lower  |      |

| Packing density              | Higher | Lower  |      |

| Wafer material cost          | Higher | Lower  |      |

| Yield (4 - micro meter)      | Equal  | Equal  |      |

| Yield (2 - micro meter)      | Higher | Lower  |      |

|                              |        |        |      |

. .

•

•

63. Fortunately, an SOS process requires fewer masking steps than a silicon-gate bulk process, which of course gives SOS a yield advantage. This advantage increases with reductions in feature size. This will probably be the determining factor in wider acceptance of CMOS/SOS circuits.

64. <u>Magnetic Bubble Memories</u>. Magnetic bubble memory devices are manufactured using techniques that are typical of the semiconductor industry at large. The heart of the device is a chip whose top surface consists of a thin film of a magnetically uniaxial material on which is deposited an array of control elements. The magnetic material has been specifically created so that its "easy" axis of magnetization is normal to the plane of the thin film.

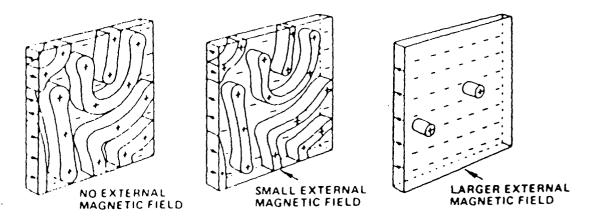

65. In the absence of any external magnetic field, the domain structure of the thin film has an antiparallel "stripe" pattern arranged, for minimum energy, to give zero net magnetism (Fig 8). If a bias field is applied perpendicular to the plane of the film, it becomes energetically favorable for the antiparallel domains to shrink.

66. When the field is increased still further, these islands contract under pressure from the applied field to form cylindrical domains. These cylindrical domains are the "bubbles". If the field is increased still further, the bubbles will totally collapse, leaving a magnetically saturated sample. Thus, binary data is stored as the presence or absence of bubbles at addressable locations.

-23-

**i** .

MAGNETIC BUBBLE MEMORY FORMATION

-

EIGURE - 8

**.** .

67. As sophisticated (and complicated) as all of this may seem, magnetic bubble memories offer an attractive alternative to other media, such as tape and disk, for reliable data storage in harsh environments. Their high packing density, ruggedness, reliability, nonvolatility, and nuclear hardness also make them well suited for military applications.

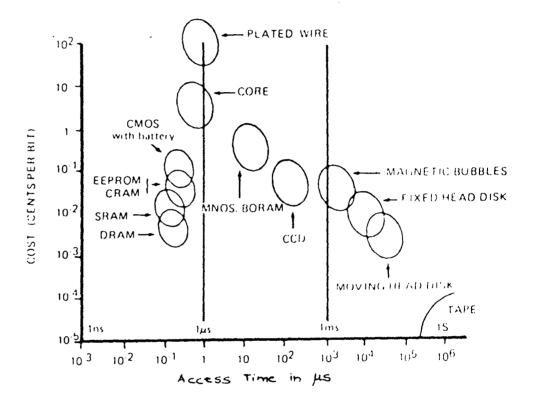

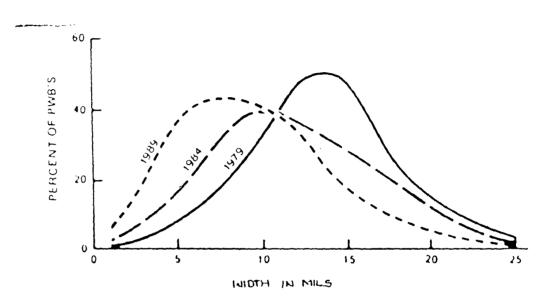

68. Although not a technical issue, cost is a key consideration when selecting a memory device. For severe environment applications, for which magnetic bubble memories are best suited, ruggedized disk, and tape drives are slower but offer a lower cost per bit (Fig 9). At the other end of the spectrum, the access times of magnetic bubble memories cannot compete with random-access semiconductor memories (RAMs).

691 Therefore, if magnetic bubble memories are to find a place for themselves in the marketplace, it will have to be in applications that can accept their slower access times or higher costs per bit in exchange for improved data security, environmental stability, radiation tolerance, and potential savings in reduced maintenance costs (Un-fortunately, although several device manufacturers have entered the field, most of them have retracted as it became evident that the technology has a smaller market than was originally predicted).

70. <u>SUMMARY</u>. There appears to be no near-term letup in the increasing capability and complexity of the semiconductor technology. In fact, if anything, the pace of new developments seems to be quickening. Added to this is the general trend

-24-

MEMORY DEVICES : COST PER BIT US ACCESS TIME

FIGURE - 9

toward having more custom and semicustom integrated circuits available to the circuit designer. These new devices offer many new capabilities to the designer, along with a more complex selection process.

71. In the past this selection process by the circuit designer was done, to a great extent, without giving major consideration to its impact on printed board technology. It was generally felt that board technology would continue to evolve to more sophistication along with advances in chip-level technology.

72. However, the new options available to the circuit designer are becoming more dependent on the cost and performance of the next-level packaging/interconnecting structure.

the cost of system integration, such as printed board 73. ÀS costs, goes up, the economics of reducing total chip count tends to push toward systems with fewer, more complex chips. There is also a general improvement in circuit performance with the use of Therefore, a final design decision as to which fewer devices. implementation of the subsystem to develop must take into account factors such as these and, hence, is not a trivial task. Therefore, the circuit designer is becoming more of a system the in designer, and vice versa, than he has been past.

-25-

#### SURFACE MOUNT ELECTRICAL COMPONENTS

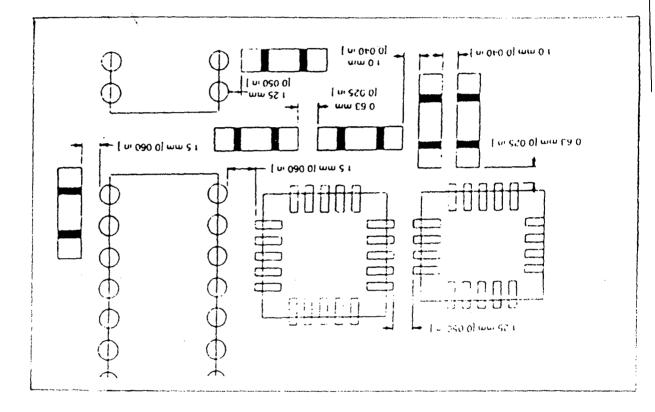

#### <u>General</u>