A CRITICAL STUDY OF COMPUTER SYSTEM PERFORMANCE EVALUATION

JAWAHA "

In Partial Fulfilment of the Requirements for the degree of MASTER OF TECHNOLOGY in ELECTRICAL ENGINEERING

by

KESAV VITHAL NORF

These hardened

Departm

INDIAN

to the Electrical Engineering OF TECHNOLOGY, KANPUR

August 1970

- to MY PARENTS

•

# CERTIFICATE

This is to certify that the thesis entitled "A CRITICAL STUDY of COMPUTER SYSTEM PERFORMANCE EVALUATION" is a record of the work carried out under my supervision and that it has not been submitted elsewhere for a degree.

V. Rajaraman Head, Computer Centre and Professor of Electrical Engineering Indian Institute of Technology Kanpur

August 1970

## ACKNOWLEDGEMENTS'

I would like to express my deep appreciation and gratitude to my thesis supervisor, Professor V. Rajaraman, for initiating me to the work presented in this report. He has found time in his busy schedule for many interesting and fruitful discussions. But for his sustained interest, guidance and kind help in innumerable ways, the work presented here would not have been possible. I cannot thank Dr C.R. Muthukrishnan enough for his academic counsel, constructive criticism and friendship.

To the viva voce committee, Professors H.N. Mahabala and M.P. Kapoor, I am indebted for their criticism and helpful suggestions.

Acknowledgements are due to Mr T. Radhakrishnan for useful discussions on analytical and simulation models for computer systems; Mr R.N. Basu for clarifying many details of operation of large third generation computer systems.

My acknowledgements are also due to : Mr H.K. Nathani for his excellent and efficient typing of the report; Mrs R. Oberoi for helping with the proofs and preparing an errata. I am grateful to the staff of the Computer Contre and friends for the very pleasant time I had during my stay here.

- Kesav Vithal Moni

August 1970

# ABSTRACT

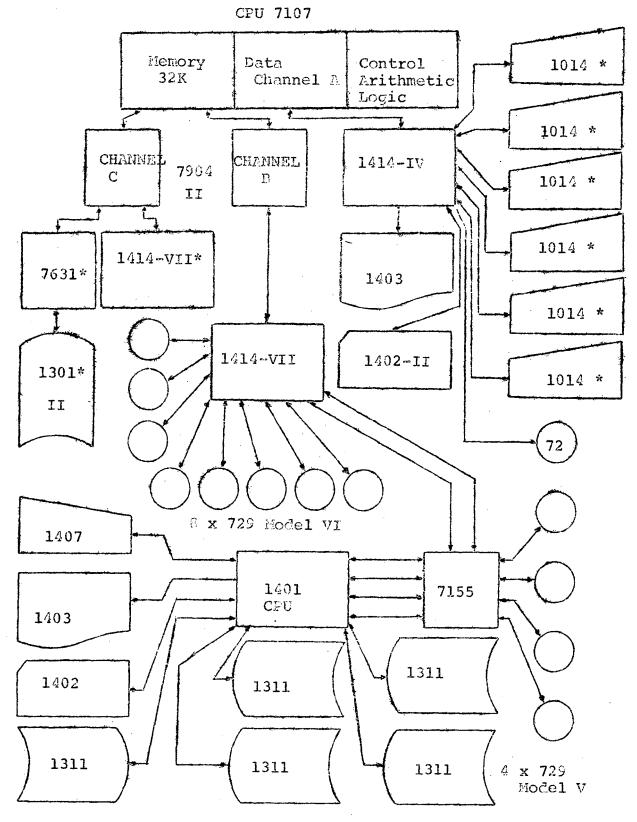

Performance Evaluation is the central problem in the study of the economics of computer systems. The problem of performance evaluation, difficulties in assessing performance, aims of performance evaluation and techniques developed to date are critically discussed. Computer systems like the IBM 7044-1401 are examined in the light of performance evaluation. Various operation schedules for the IBM 7044-1401 are proposed and compared. A software monitor to obtain the user job profile is outlined and a model to compare configurations of this system is proposed.

# CONTENTS

.

CERTIFICATE

ABSTRACT

# ACKNOWLEDGEMENTS

| CHAPTER        | I   | INTRODUCTION                                                    | 1          |

|----------------|-----|-----------------------------------------------------------------|------------|

|                |     | 1.1 Motivation for assessing performance<br>of computer systems | 1          |

|                |     | 1.2 The problem of performance evaluation                       | 11         |

|                |     | 1.3 Aims of performance evaluation investigations               | 16         |

|                |     | 1.4 Obstacles to performance evaluation                         | 19         |

| <b>.</b>       |     | 1.5 Some measures of performance                                | 21         |

|                |     | 1.6 Scope of work reported                                      | 24         |

| CHAPTER        | ·II | ANALYSIS OF COMPUTER SYSTEMS FOR<br>EVALUATIVE STUDIES          | <b>2</b> 6 |

|                |     | 2.1 Analysis of digital computer<br>computer hardware           | 27         |

|                |     | 2.2 Analysis of the operating systems                           | 59         |

|                |     | 2.3 Analysis of workload                                        | 82         |

|                |     | 2.4 Conclusions                                                 | 95         |

| <u>CHAPTER</u> | III | SIMULATION TECHNIQUES FOR COMPUTER<br>SYSTEM EVALUATION         | 98         |

|                |     | 3.1 Introduction                                                | 98         |

|                |     | 3.2 Introduction to simulation languages                        | 100        |

|                |     | 3.3 Motivation for simulation of<br>computer systems            | 105        |

|                |     | 3.4 Classification scheme for various simulation models         | 109        |

|                |    | 3.5 Difficulties in simulating<br>multi-processor computer<br>systems          | 117  |

|----------------|----|--------------------------------------------------------------------------------|------|

|                |    | 3.6 Acquisition of data for assessing system performance                       | 1.24 |

|                |    | 3.7 Conclusions                                                                | 127  |

| CHAPTER        | IV | STUDY OF EVALUATIVE PROBLEMS FOR THE<br>IBM 7044-1401 COMPUTER SYSTEM AT IIT/K | 129  |

|                | k  | 4.1 Computational resources at IIT/K                                           | 130  |

|                |    | 4.2 Operation schedules for IBM 7044-<br>1401 at IIT/K                         | 133  |

|                | •  | 4.3 Models for IBM 7044 computer system                                        | 142  |

|                |    | 4.4 Specification of a software monitor<br>and a technique for implementation  | 148  |

|                |    | 4.5 Conclusions                                                                | 154  |

| <u>CHAPTER</u> | V  | CONCLUSIONS AND SUGGESTIONS FOR<br>FURTHER WORK                                | 156  |

|                |    | 5.1 Summary and conclusions                                                    | 156  |

|                |    | 5.2 Suggestions for further work                                               | 158  |

|                |    | REFERENCES                                                                     | 159  |

,

.

ii

#### CHAPTER I

#### INTRODUCTION

Electronic digital computers have been in existence for just over two decades. From early beginnings, like the ENIAC in 1946, successive developments in speed, size, versatility and usage of computer systems have been rapid, especially in the last six years or so. Today, in the industrially advanced countries of the West in particular, computers have pervaded many spheres of human activity and endeavour. Surprisingly enough, the design, usage and the economics of computers is yet far from an exact science; the art of computer programming is one such glaring example. The study of one of these aspects, the economics of computer systems, forms the main theme of work reported here in this thesis.

# Section 1.1: Motivation for assessing performance of computer systems

The study of the economics of computer systems necessitates a detailed study of factors that affect their manufacture, operation, maintenance, application and utilization. Hence motivation for improvements and innovations in computer system architecture, system design and software support can be tracked to the economic benefits or trade offs obtained. A brief review of major advances in computer systems is therefore in order.

The evolution of computer systems is a well reported topic in literature. To quote a few, Richards [1], Hassitt [2] and Rao [3] have given excellent accounts of it in their works. Therefore, no attempt is made here to elaborate on this subject or trace its history. However, certain developments relevant to the subject of study are outlined here; their understanding constitutes some of the requisites for the study of the economics of computer systems. It may be noted in passing that terms like evaluation, performance, workload have to be defined in the context of computer systems and will be elaborated upon in the next section.

Advances in computer hardware can be categorised as shown below:

- (i) Technological advances in terms of device speeds, reliability etc.

- (ii) Advances in logical organisation. Specifically, the development of interrupt facility, memory protect feature and over-lapped input/output operations by use of data channels which together provide for non local concurrency in the operation of the computer system. The introduction of instruction look ahead and memory hierarchy in primary storage provide local concurrency in operation.

Advances in computer system software fall into two classes:

(i) the development of programming aids through the formulation of user oriented, procedure and problem oriented, programming languages;

(ii) and the development of operating systems [4,5,6].

The latter is of interest; it provides a logical environment in which the user may conduct his work and it allocates him the necessary resources to accomplish the work. Important features of an operating system are:

(i) file management [7] and input/output control;

(ii) segmentation [8] and memory management;

(iii) multiprogramming, time sharing and processor allocation

[9, 10, 11, 12, 13, 14].

As is evident from these developments, a present generation computer system is an integrated complex of hardware and software resources which afford the user necessary facilities for problem solving. An analysis of such a system, in the light of various economic factors imbibed in their design, should provide the necessary motivation for the ensuing study of this subject. The outlook that computer systems are a collection of hardware and software resources has its advantages. The motivation of the manufacturer to produce such systems and the study of resources to be allocated to the user to suffice his needs are both presented in a uniform manner.

Hardware resources of the computer system are an aggregate of the following:

- (i) computational resource provide by the comprehensive and powerful instruction repertoire of the central processing unit;

- (ii) memory resources for program and data storage provided by the main memory;

- (iii) a hierarchy of auxilary storage, for storing large volumes of information, provided by peripheral storage devices operating over a large range of information transfer rates; in general their storage capacity is inversely related to their information transfer rate;

- (iv)facilities for communication between the main memory and the peripheral auxilary storage devices, provided by the data channels and device controllers or interfaces;

- (v) and facilities for communication between the user and the computer system, provided by the host of ever increasing input/output devices.

The underlying philosophy in the design of hardware is to achieve modularity, compatibility, adaptability and reliability in computer systems. To a certain extent, these factors have been motivated by economic considerations.

Modularity in system design allows interchangebility of system components or subsystems and flexibility in their interconnection. This means that virtually any desired system can be assembled. Compatibility has given scope to the development of a whole line or family of computer systems with very nearly the same machine language. Such computer systems are upward and downward compatible. This means that the same machine language program can be run or executed on any computer system in the family. It is therefore an easy matter to upgrade or downgrade the system depending on the changes percieved in the workload. Consequently, effort in recoding of already available or developed software is kept to a minimum, if not absent altogether. Therefore, modularity and compatibility make it possible to most economically configure any computer system of desired size and speed or change the system to suit changes in demand with least expenses incurred.

The usage of computers for a wide range of applications is enhanced by those features in system design which permit ease in adapting the system resources to the needs of the application on hand. A good example of adaptability in system design is the basic unit of storage in the IBM system/ 360: the eight bit 'universal' byte. This eight bit byte stores a character, two decimal digits and of course eight binary bits of information. This facilitates character handling,

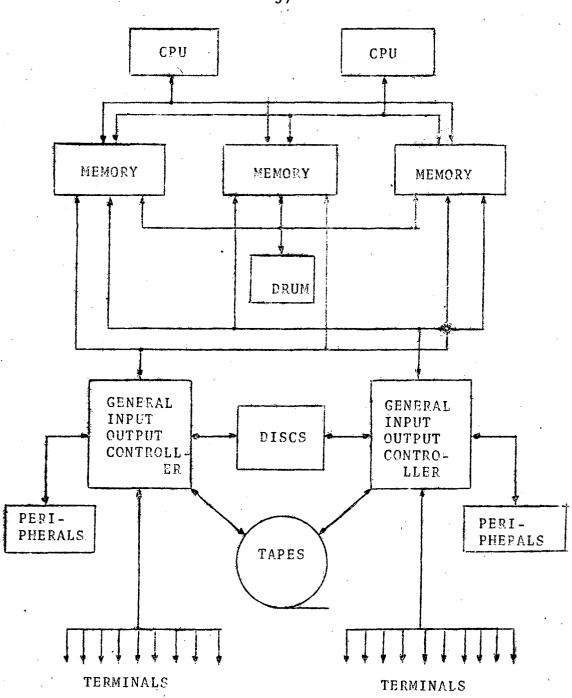

decimal arithmetic and binary arithmetic and high utilization of main memory. Therefore, this 'univeral byte' can be easily adapted to any type of application. Such features result in good dividends as the manufacturer does not have to produce several different systems to cover the range of applications. Reliability in computer systems is an outcome of technological progress and redundancy in system design. This feature has made possible, among other things, the space exploration mission and is absolutely necessary for the development of a 'computer utility'. Configurations of the IBM system/360 Model 67 [15] and the MULTICS System [11] embody all these principles and illustrate the extreme complexity of hardware that is now possible with present day technology.

Stand alone hardware resources cannot provide the necessary problem solving environment to the user. In fact, the user works only on a virtual machine presented him by the operating system. Saltzer [16] gives an interesting illustration of the virtual machine seen by the user of the MULTICS System. The operating system shields the user from the details of hardware and its limitations and offers the user a logical environment for programming his problems. Hence, software resources available to the user are analysed in the following paragraphs. These resources are:

- (i) a number of language processors which simplify

his programming burden by giving him the power

to express procedures for solution of his problems

in a manner akin to his way of thinking;

- (ii) a large program library providing the user with 'ready made' debugged program packages which perform commonly needed functions;

- (iii) a filing system which facilitates the creation, editing and retrieval of large files of information;

- (iv) and a set of procedures which allocate to the user any of the system resources as he needs them.

The main features in the design of the afore-named software resources are:

- (i) features to attract and cater to the needs of a large user population and creating a machine or hardware independent environment to the user;

- (ii) and incorporation of proper resource allocation algorithms which are to ensure an efficient utilization of the overall system and provide the best grade of service.

It is seen that economic benefits that arise from the various considerations in hardware design are very easy to point out. They are very tangible in the sense that quantitative assessment of trade offs obtained is possible. This is not the case with the benefits gained by use of software. Questions can be raised about the increase in efficiency of programming by use of higher level languages. Studies of the behaviour of programmers, in terms of time taken to develop programs for given problems, when programming in different environments and having different type and amount of interaction with the computer system, have been conducted and these results summarised [17]. Answers to such questions and results of such studies are difficult to evaluate as they are subjective in nature. It is apparent that there are many such problems in assessing the utility of software. Nevertheless, the benefits accrued from software are obvious even though not quantifiable.

Usage of computers is costly. Resource allocation by the operating system is therefore an important aspect of the tasks to be performed by it. Performance assessment of computers and hence the evaluation of various techniques of resource allocation indeed invite attention.

The design of computer systems described in the preceeding pages is always open ended so as to leave room for future developments. It should be clear by now that the extent of analysis to be carried out before the design of computer system hardware and software is quite

tremendous and these analyses contribute greatly to the economics of manufacture of computer systems and their usage. Experience about the performance of such systems prove invaluable for the design of future systems.

Amongst the many other problems in the area, the selection of computers and the pricing of computer services have evinced interest and are worth mention. Joslin [18] and Sharpe [19] have discussed problems associated with computer selection. The main problem in . the selection of computer system is the evaluation of tenders and contracts offered by the manufacturer or the vendor. Trade offs between rental costs and purchase costs have to be estimated. The main components of rental costs are the Basic Monthly Rental charges, the Extra Usage charges and the Maintenance charges. On the other hand the break up of costs in the purchase of computer systems is the Purchase charges, and the Maintenance charges. There are several hitches in the comparison of competitive effors. The first difficulty is in estimating accurately the expected or projected workload, which the computer system in question is expected to service. Secondly, to find procedures to estimate quantitatively, criteria for performance of the computer system in the light of the workload. On overcoming these problems, the comparison of various rental contracts

and purchase terms can be obtained. The types of contracts offered have been discussed by Sharpe and he proceeds to conduct an initial analysis of the relationships between the various costs quoted in them. Other issues in computer selection have been reviewed by Sharpe and Joslin. Certain periodicals like Datamation and Computers and Automation bring out articles frequently on related topics. As they are numerious and the material presented in them is not the central theme here, reference to such works are omitted.

Two problems are prominent when pricing computer services The first is to fix the price for usage of the computational facilities and type of service given. These issues clearly necessitate the evaluation of performance of the computer system. The second problem is one of the devising proper accounting schemes for logging the actual usage of system resources by the user [20]. The log, besides being useful in accurately billing the user, provides a rich source of information about user characteristics.

Problems of maintenance, of operation, of management and personnel for manning computer installations also come under the investigations in the economics of computer systems. As is evident from the nature of all the issues raised so far, a number of subjective criteria will play an important role in the final solution of any of these issues.

At this stage, it is quite apparent that the solutions to the afore-mentioned problems depend on the evaluation of performance of computer systems. Due to the central character of performance evaluation in the study of the economics of computer systems, this is the only problem considered at length in this thesis. The problem of imposing economic constraints on the performance of computer systems in order to solve other problems mentioned is considered secondary here.

# Section 1.2: The problem of performance evaluation

The word 'performance' means the manner or success of working or the execution of a task. The engineering sense of the word is related to efficiency. And by efficiency is meant the power to produce the intended result; for most purposes, it is the ratio of machine's output of energy to its input. Unfortunately, the usefulness of computer is in no way related to the energy they consume to produce the intended result. They deal with a volatile and intangible commodity that information is. Therefore, the normal usage of words like efficiency and performance do not apply to computer systems.

It is well known that computers can deal with only those problems in which quantification is possible, even through mere coding. The study of computation as an

abstract entity is a hot topic of current research. And this effort is unfortunately not addressed to the problem of quantification of computation as in the context of a general purpose computer. A machine independent measure for computation is therefore not a reality as of now. Hence, it is noted regrettably, 'performance' of computer systems has not yet been defined in a machine independent manner.

Be that as it may, in the absence of rigour concerning the fundamentals of this area of computer science, and for the lack of a better word, performance of computer systems will be conveniently assumed to be their 'behaviour' in the execution of 'workload' presented them by the users. Several criteria for 'behaviour' of the computer systems have been proposed; examples are the utilization of system components, service rendered to users, time taken for given tasks or just a trace of the operation of the system. The 'workload' of a computer system is much more difficult to define. For the purposes of this thesis, the workload of a computer system is defined in terms of statistical measures of factors that are deemed to affect system performances. Performance evaluation of computer systems is thus a set of techniques for relating user requirements (the workload) to the capabilities of the computer system in the context of such criteria as explained above.

Two types of investigations are undertaken in performance assessment or performance evaluation of computer systems. The first concerns the study of the sensitivity of the behaviour of the computer system with respect to certain system parameters. Examples of system parameters could be the configuration of the computer system or the various resource allocation algorithms in the operating system. Such studies are directed towards improvement of the behaviour of the system for a given workload. Hence the effectiveness of certain features of system design are examined. In so far as the relationships between various aspects of the computer system and its operation are not well understood, this type of investigation may be carried out merely to gain insight into these matters. Most of the effort in performance evaluation has been of this type.

The second type of performance evaluation study is one concerning comparison of different computer systems for a given workload. Due to the fact that the workload of the computer system too has not been defined in a machine independent manner, this problem is much more difficult to tackle than a problem of the first type. However, this is an important problem to solve in order to compare various approaches to system design on a common footing.

With this background, it is appropriate at this stage to ponder about desirable characteristics of performance evaluation techniques. In essence, performance evaluation entails the following:

- (i) characterisation of user workload, the jargon is user job profile, in a machine independent manner;

- (ii) definition of suitable criteria for the behaviour of the computer system:

- (iii) imposition of software constraints on user job profile to obtain the actual work to be done by the hardware system;

- (iv) determining the behaviour of the system and hence quantitatively finding the values of various criteria set forth earlier by using the above.

No performance evaluation technique really attempts a clear and detailed solution of the problem as outlined above. The difficulties faced in evaluating performance are many, their discussion is held over to a later section.

Techniques of performance evaluation have had early beginnings. In the late 1950's, such techniques were developed to aid in the system design of Project STRETCH. But it is only in the last few years that such efforts have gathered force. The interest they have aroused is evident from survey papers on performance evaluation by Calingaert [21], Meredith Smith [22], Wickens [23] and Drummond [24]. As the problem covers many facets and activities of computer systems, these surveys have not done full justice in bringing out the nature of the problem in its entirety. However, they have succeeded in pointing out various difficulties faced when seeking solution to the problem and have given a broad classification of efforts in this direction to date.

Performance evaluation techniques are concerned with the modelling of computer systems and users. Rather than modelling the computer system or the user in complete detail, most of these techniques only attempt to study one aspect of the user demand and system behaviour at a time. Modelling has been done either by means of analysis, analytical or otherwise, of computer systems and users or by use digital computer discrete system simulation techniques. These efforts are discussed in the succeeding chapters.

Other characterstic features of techniques of assessing performance of computer systems are:

- (i) the techniques give an absolute or relative measure of performance,

- (ii) the methods give a measure of potential or actual performance.

# Section 1.3: Aims of performance evaluation invagtigations

The preceeding sections present an intuition for performance evaluation of computer systems. It is worthwhile to consider for the sake of completeness, what the aims in assessing performance could be. As pointed out earlier, a number of subjective values creep into the solution of issues raised earlier: it follows naturally that the aims of an evaluative study are subjective. It is not possible to present these issues in any measure of completeness due to lack of experience and as such information is not readily available. However, to lend some clarity in specifying the objectives of assessing performance of computer systems, a perfunctory classification and analysis is attempted.

Obviously, the aims of assessing performance of computer systems depend on the group of people conducting the evaluative study. These groups can be broadly classified into the following catagories:

- (i) the 'user group' which comprises people interested

- in the selection of suitable computers;

- (ii) the 'systems group', comprising system analysts

and system programmers;

- (iii) and the 'manufacturers group', competitors in the computer industry who want to stay in business!

What follows is an attempt to analyse the interests of each group and hence arrive at some of their objectives in performance evaluation and the type of techniques they need.

The user group is interested in acquiring a computing facility which will suffice their needs. Unfortunately, it is not easy, even for the experienced user to define or specify the expected workload. This point will be amplified in a later section of this chapter. Assuming that the workload has been estimated, the strategy for selection would depend on the cost per unit work, the overall cost and the grade of service offered to the various priority groups in the user community. To this end the user group would have need for the following techniques.

- (i) Procedures to estimate workload that the computer system is expected to service and projection of load growth in years to come.

- (ii) Procedures to estimate trade offs between hardware and software available in the light of the defined workload.

- (iii) Procedures to determine suitable mode of operation.

- (iv) Procedures to estimate the grade of service to be expected.

- (v) Procedures for comparing performance of various configurations of a computer system for the defined workload and comparing various computer systems to the same end.

If the above considerations are quantitatively worked out for eligible systems then the final choice made is a compromise between economic constraints and trade offs available with extra investment.

The systems group is directly concerned with the management of the computer system. Their interests are primarily in affording a powerful computer service to the user community and ensuring the maximum utilization of the system resources. Naturally, details of the computer system resources indicated in the preceding section are of immediate interest to them. Their purpose in performance evaluation would be:

- (i) to compare various resource allocation algorithms,

- (ii) to compare software packages

- (iii) and to develop new techniques for the above in

- order to provide better service or improve system utilization.

This group will find it essential to monitor the operation of the system so as to obtain information to do the above tasks. Trade offs between system utilization and service rendered to the user community are chief factors of interest in their performance evaluation studies.

The interests of the manufacturers group are only too well known. Their aim is to maximize the returns on their investments. Besides, they have to survive in a

competitive market. This group might have for its objectives in performance evaluation the following:

- (i) measurement of improvement in performance due to the introduction of new hardware features;

- (ii) comparison of their computer system with those manufactured by competitive firms;

- (iii) development of software features in order to attract users.

In order to accomplish the above, a survey of current and projected applications of computer systems and their relative importance in the market is necessary. Techniques need be developed to achieve the same.

Section 1.4: Obstacles to performance evaluation

In the preceeding sections, the problem of performance evaluation and techniques necessary to accomplish it were sketched in simple terms. Questions raised in this connection are either fundamental in character or examine details of design features and operation of computers. Illustrations of questions of a fundamental nature are: for the purposes of system performance, what does a job or task or application mean? and how does it load the system resources? Examples of questions regarding details of design or details of operation for evaluative studies are: what improvement in performance can be expected by the introduction of a scratch pad memory or an instruction look ahead feature? Or, what scheduling algorithm should be used for processor allocation in a time shared, multi programmed environment? Questions similar to the latter two are quite objective and much fruitful analysis has been done in solving such problems. The chief difficulties in performance evaluation are in obtaining answers to questions of the first type and these are considered in the following paragraphs.

An automaton is said to be universal in computation if it can perform the mapping specified by any 'computable' function. Digital computers are engineering approximations to automata exhibiting this property of universality in computation. In the same vein, computer programs are indeed engineering approximations to the specification of the computable functions and they normally have limitations as to the range of data they can handle for any given it is seen that results from the problem. Therefore. Theories of Automata, Formal Languages and Computation are not useful in describing programs for the pragmatic purpose of defining the workload of computer systems. This situation behoves the development of a different attitude towards programs and computers. A more detailed look at what might this attitude be is necessary and is presented in a later chapter. It suffices to stress here that as of now there exists no precise formulation or quantification of user requirements.

A consequence of this state of affairs is that the user machine interface is ill defined, be it a language or a device. This is evident from the ever increasing number of user oriented languages and 'tailormade' input/output devices being designed. Also, there exists a lack of accepted standards and hence communication between various levels of people interacting with the computer system is greatly hampered. All this stems out of the fact that the study of computers is more of an art than a science at present.

Besides these difficulties, there are some technological difficulties in conducting a performance evaluation study. For example, the dynamic measurement of data of all types within a computer system so as to determine its behaviour or characterise the user job profile is not always possible with available tools like hardware or software monitors. However, these problems will be hopefully overcome in the near future. At the University of California, Los Angeles, it is reported that the operation of several computers, including the IBM System/360 Model 67, is being monitored by a SDS Sigma 7 computer! Information obtained from such experiments should prove interesting indeed.

Section 1.5: Some measures of performance

ГН - 31,52

In this section, the concept of 'behaviour' of the computer system is elaborated upon by defining some measures or criteria for assessing computers system Thus

> 681.3.06 N 774

performance. At the outset it must be made clear that the actual computation of values for some of these criteria may not yet be possible due to difficulties outlined earlier. Again, for similar reasons, it is easier to evaluate these criteria for a computer system with change in some system parameters than for different computer systems. A few of these measures are abstracted here from the multitude devisable as the goals of evaluation of computer systems are subjective. Some of these measures are more suited to a batch processing environment and others to a time shared mode of computer operation. They are the following:

- (i) Throughput. This is a measure of the steady state state capacity of the system. In other words, it refers to the volume of work done in an accepted unit of time. Constrained by cost, this is the most objective performance criterion to those managing the system.

- (ii) Turnaround or average response time. This represents the average the average time between the receipt of a specific service request of a user by the sytem and the satisfaction of that request at the terminal or to the user. Again, constrained by cost, this is the single most useful measure of performance to a user.

- (iii) Average waiting time. This measure is an indication the load in each priority group of the user population and time required to service the group.

- (iv) Average queue length. This measure is linked with the average waiting time and indicates the load for each priority group. The relationship between allocation of priorities to user groups and their effect on these measures merits attention.

- (v) Availability. This criterion concerns the number of hours, excluding maintenance and breakdown, the computer system is available for use. It is a measure of the percentage of total time the system is in service for user programs.

- (vi) Reliability. This measure indicates the frequency of hardware and software failures and is measured as the mean time between hardware failures or mean error free time.

The mentioned measures of performance are the quantitative end results of an evaluative effort. The goals of performance evaluation themselves can be realised in terms of the criteria mentioned above. These are not all the useful measures; more will be introduced at appropriate stages in succeeding chapters.

## Section 1.6 Scope of work reported

Literature on computer system performance evaluation is scattered over a wide spectrum of technical journals. An exhaustive survey of all literature has not been possible. Instead, a cogent and uniform treatment of problems of performance evaluation is presented here. Motivation for particular approaches to the solution of these problems and classification schemes for techniques developed or studies conducted is also given in this report.

In Chapter II are discussed various analyses of computer systems for the purpose of performance evaluation. They are, the analysis of computer hardware, the analysis of operating systems and the analysis of workload. The usefulness and limitations of certain techniques for comparison of computer hardware are brought out. As an illustration, sample calculations are made for comparison of central processing units by the instruction mix technique. In the discussion on operating systems, attention is restricted to the various resource allocation algorithms. In view of the preceding analyses, a quantification of workload is attempted.

Chapter III embodies an introduction and review of simulation techniques for the study of computer systems. In order to compare different techniques of discrete system simulation, the GASP II A simulation package was debugged

and implemented in the IBSYS operating system of IBM 7044. (Earlier, GPSS III was the only available programming system for discrete system simulation.) Motivation for use of simulation techniques, classification of simulation experiments and a comprehensive look at difficulties faced when using this technique are the main features of this chapter. Chapters II and III form a critical state-of-the-art appraissal of computer system performance evaluation.

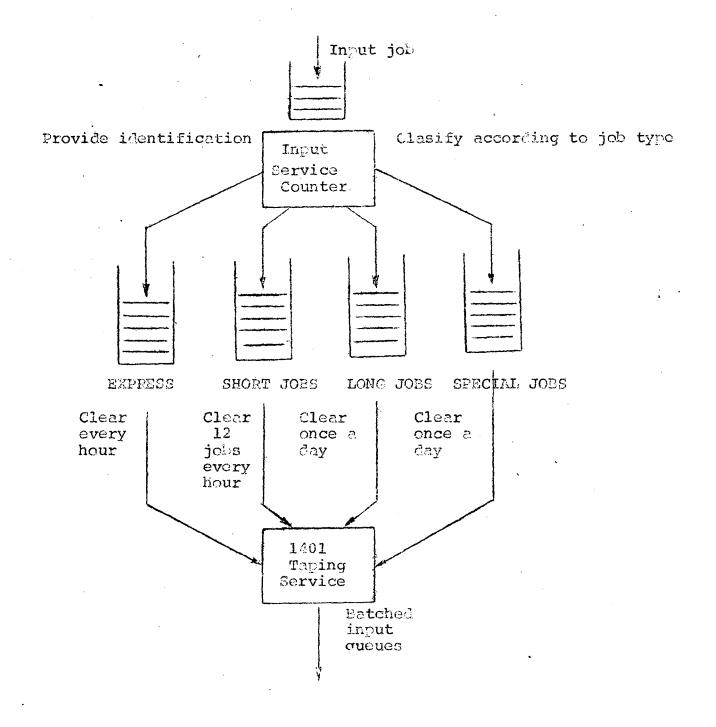

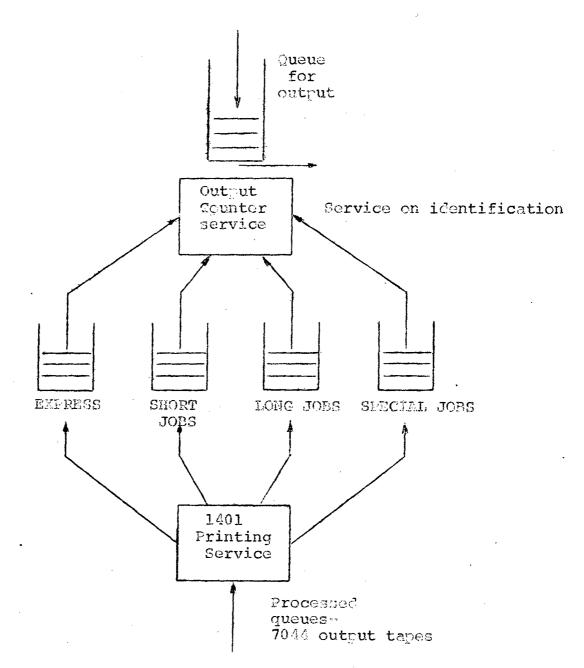

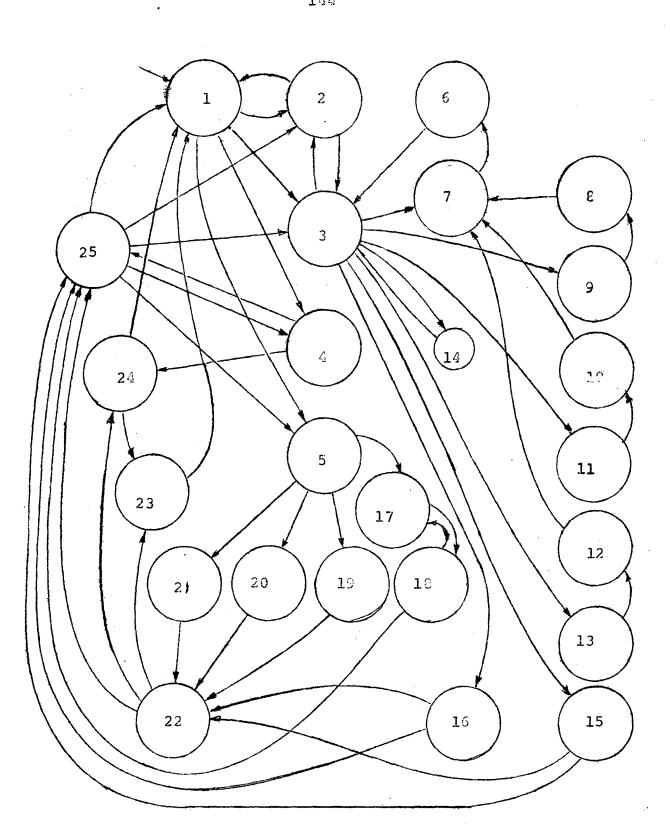

Batch processing computer systems with off line satellite systems to manage show peripheral work - in particular the IBM 7044-1401 computer system at Indian Institute of Technology, Kanpur - are examined from the point of view of performance evaluation in Chapter IV. Operation schedules for such systems are discussed in relation to throughput and turnaround. These operation schedules were implemented for the IBM 7044-1401 systems. Next, models are proposed for this system. Of particular interest is a model which takes care of parallel input-output operations. This model should prove useful in the evaluation of several configurations of a system for a given workload. No pragmatic evaluative work is possible till statistics to characterise user workload are gathered and the system studied in relation to this workload. Therefore, the requirements of a software monitor to achieve this and techniques to implement the same are outlined.

The concluding chapter, Chapter V, contains suggestions for further work and mention of problems not discussed here.

#### CHAPTER II

# ANALYSIS OF COMPUTERS SYSTEMS FOR EVALUATIVE STUDIES

The analysis of computer systems from the standpoint of performance evaluation can be categorised in the following manner:

- (i) Analysis of computer hardware facilities and logical organisation. The purpose of this analysis is to examine various hardware features and their contribution to system performance in the light of the workload.

- (ii) Analysis of the operating system. Two aspects of the operating system are of interest. First, the features of the virtual machine offered to the user. And second, the effectiveness of various resource allocation algorithms in terms of utilization of system resources in presenting the user this virtual machine. Of special interest is the 'overhead' incurred in providing the virtual machine and in allocating the system resources. Here, 'overheads' are understood to mean the utilization of system resources by the system itself in order to provide this virtual

machine to the user.

(iii) Analysis of workload. The workload of a computer system is a composite of user demands of system resources and the overheads incurred in offering these resources to the user. An attempt is made to clearly delineate these two components of the workload and characterise the user workload in terms of its demand on the system resources.

In this chapter, various attempts at such analyses will be reviewed. Problems yet to be tackled are pointed out and wherever possible a brief qualitative analysis will be included.

Section 2.1: Analysis of digital computer hardware

Computer system hardware is a collection of resources like the Central Processing Unit (CPU), main memory space, input/output channels, auxilary memory, communication links and input/output devices. The analyses of these resources will be qualitative as information about details of their design is not forthcoming. The study of their interconnection is even more intriguing. The latter indeed poses a very challenging problem in performance evaluation and is the central issue in the study of computer structures. It is hoped that the analysis of computer hardware will aid in the characterisation of workload attempted in a later section.

The CPU is the most complex subsystem in computer hardware. In the following discussion, the CPU is considered only as a computational resource. Hence, for the purposes of performance evaluation, the main features of the CPU are the instruction repertoire, local and non local concurrency and the data path between the CPU circuitry and the main memory. Main memory space is a system resource by itself and the study of user demands on it will be considered separately.

The instruction report instruction set', offers a computational facility to the user. The execution of these instructions requires a wide variety of operations ranging from simple CPU register manipulations to complicated arithmetic operations. In general there are two phases in the execution of an instruction: the instruction decoding phase and the operation Time taken to decode an instruction is a function of phase. the length of the instruction and the generation of the effective address of the operand. And the time for the operation phase is related to the number of operations to be performed. In some present day computers these operations are realised as sequences of micro-operations. Through proper design of instruction codes and micro-operations, the user is given the flexibility to set up non-standard instructions to perform often needed functions. Such a feature is called 'micro program control' and it uses a 'wired in logic' or 'read only memory. Systematic design of instruction sets is possible

due to such features in system design.

Instruction sets of computers are modular. The manufacturer offers the machine with a 'basic instruction set' or an 'extended instruction set'. The extended instruction set offers useful instructions for particular type of applications. For example, instructions for variable length operations are needed in commercial data processing operations and floating point, double precision arithmetic instructions for use in scientific computations. The need for powerful instructions is therefore seen to arise from the frequency of occurrence of certain types of operations in typical applications.

A measure of effectiveness of the computational resource for a particular type of application is the average instruction time. An arithmetic mean of all instruction times does not suffice for the simple reason that the nature of the application or workload is in no way reflected in the average obtained. Weighted instruction times are more suitable for obtaining the same. The weights assigned to each instruction in the instruction set could for example be simply computed from the frequency of occurrence of that instruction in the workload. As the instruction set of computer system can be quite extensive, instructions are grouped into classes by the operations they perform and the time taken to execute them. Weights are assigned to each of these classes by frequency of occurrence of instructions in the class. Weighted groups as described

above are termed as 'instruction mixes'. Put another way, if there are n groups of instructions with weights  $W_1, W_2, \ldots, W_n$ and with execution times  $T_1, T_2, \ldots, T_n$ , then the average instruction time is:

where

i=n  $\Sigma$   $W_i=1$  and  $W_i \ge 0$  for all i [21,22]. i=1

Instruction mixes are very simple to deal with but very difficult to define. That is, the grouping of instructions into classes and assigning weights to them is not at all an easy thing to do. Firstly, a dynamic instruction-trace of the workload must be available. The instruction-trace of a program can be anything between 50 to 100 times slower than the actual execution of the program. And hence a few minutes of 'typical' computation is actually traced in practice and an instruction mix is defined using this data. Secondly, there is no standardization of the instruction set yet. In fact, each machine is empowered with some special instructions for simplifying computation of a particular type of application and this feature cannot be reflected in an instruction mix.

The implication of the above is that it is difficult to compare CPUs of two different computer systems using just an instruction mix. It is seen that the speed of execution of instructions is a function of several factors mentioned earlier, notwithstanding the memory speed. Hence comparison of CPUs which differ in any of these factors by using instruction mixes can give misleading results. However, comparison of CPUs with similar features by this technique can be quite fruitful.

Some of the well known instruction mixes for scientific computation are the Arbuckle Mix [25] and the Gibson III Mix [22]. As an illustration, the Arbuckle Mix is given in Table 2.1 and a Commercial Mix [22] is given in Table 2.2. Also shown in tables computation of average instruction time obtained is the by use of these mixes, for IBM 7044 system. It should be noted that the group of instructions in the 'miscellaneous' category of the Arbuckle mix is really an instruction mix in itself. For the sake of simplicity, the fixed point add instruction time is used as the computation time for this category. The reason for this is that the fixed point add instruction requires both the instruction decode phase and the operate phase which uses the sophisticated circuitry of the CPU. Hence, main memory speeds and CPU arithmetic speeds are both reflected in the fixed point add In the computations for evaluating the commercial mix, it time. should be noted that operations rather than instructions have been specified. Sequences of instructions to realise these operations have therefore been used.

|                            | FREQUENCY        | IBM 7044                  | TIME ON IBM       |

|----------------------------|------------------|---------------------------|-------------------|

| INSTRUCTION                | OF<br>OCCURRENCE | INSTRUCTION $\mu$ SECONDS | 7044<br>μ SECONDS |

| Floating point add         | 9.5              | 11.0                      | 104.5             |

| Floating point<br>multiply | 5.6              | 20.0                      | 112.0             |

| Floating point<br>divide   | 2.0              | 36.0                      | 72.0              |

| Load/Store                 | 28.5             | 4.0                       | 114.0             |

| Indexing                   | 22.5             | . 4.0                     | 90.0 ·            |

| Conditional branch         | 13.2             | 2.0                       | 36.4              |

| Miscellaneous              | 18.7             | 4.0                       | 74.8              |

|                            |                  | • •                       | 593.7             |

Average instruction time for IBM 7044  $\pm$  5.937  $\mu$  seconds

Table 2.1: The Arbuckle Mix for scientific computation and sample calculation of average instruction time for IBM 7044.

| EXTENT       | WEIGHT                                                        | IBM 7044<br>TIME FOR<br>1 OPERA-<br>TION µSEC                                                                                                                                                                                                      | TOTAL TIME<br>ON<br>·IBM 7044<br>µSEC                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | 9                                                             | 10                                                                                                                                                                                                                                                 | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2            | 5                                                             | 16                                                                                                                                                                                                                                                 | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3            | 7                                                             | 18                                                                                                                                                                                                                                                 | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6            | 1                                                             | 10                                                                                                                                                                                                                                                 | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10           | 1                                                             | 26                                                                                                                                                                                                                                                 | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12           | 3                                                             | 20                                                                                                                                                                                                                                                 | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1            | ì                                                             | 10                                                                                                                                                                                                                                                 | 10,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10           | 1                                                             | 36                                                                                                                                                                                                                                                 | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 60           | 2                                                             | 44                                                                                                                                                                                                                                                 | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Taken        | 15                                                            | 2                                                                                                                                                                                                                                                  | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Not<br>Taken | 13                                                            | 2                                                                                                                                                                                                                                                  | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| -            | 2                                                             | 4                                                                                                                                                                                                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|              | 40                                                            | 4. ·                                                                                                                                                                                                                                               | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              | -<br>-                                                        | 100                                                                                                                                                                                                                                                | 756                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              | 1<br>2<br>3<br>6<br>10<br>12<br>1<br>10<br>60<br>Taken<br>Not | 1       9         2       5         3       7         6       1         10       1         12       3         1       1         10       1         10       1         60       2         Taken       15         Not       13         Taken       2 | EXTENT       WEIGHT       TIME FOR<br>1 OPERA-<br>TION µSEC         1       9       10         2       5       16         3       7       18         6       1       10         10       1       26         12       3       20         1       1       10         10       1       26         12       3       20         1       1       10         10       1       36         60       2       44         Taken       15       2         Not       13       2         2       4       40 |

Average instruction time for IBM  $7044 = 7.56 \mu$  seconds Table 2.2: A commercial mix and sample calculations for IBM 7044

Gross comparison of computational power of CPUs belonging to a family of computer systems like the IBM System/360 series or the ICL 1900 series is very easy, by using this technique. The average instruction time: , for scientific and commercial workloads, for some word oriented computer systems is tabulated in Table 2.3. A word of caution is necessary when considering figures for average instruction times given in the table. Due to lack of familiarity with assembly language programming in PLAN (for the ICL 1900 series) and unavailability of correct information regarding usage of special features provided, the average instruction times for commercial computations could be conservative. Computation of this time for some bigger members of this family was not possible due to incomplete information given in the ICL 1900 series introductory text. No computation of average instruction times could be under taken for models of the IBM System/360 series, other than Model 44, due to unavailability of their functional characteristics. As all the computer systems compared in this table are word oriented and have some features in common, the average instruction times give a fair idea of their relative computational power.

|                                                             |                          | 35                              |                                     |       |                                                   |                                     |

|-------------------------------------------------------------|--------------------------|---------------------------------|-------------------------------------|-------|---------------------------------------------------|-------------------------------------|

| 3                                                           |                          |                                 |                                     | ··    |                                                   |                                     |

| COMPUTEP<br>SYSTEM                                          | MEMORY<br>SPEED<br>U SEC | FLOATING<br>POINT<br>OPERATIONS | STORAGE TO<br>STORAGE<br>OPERATIONS |       | INSTRUC-<br>TIMEµ SEC<br>ial Arbu-<br>ckle<br>Mix |                                     |

| IBM 7040                                                    | 8.0                      | H.                              | Н                                   | 22.48 | 15.41                                             | Code                                |

| IBM 7044                                                    | 2.0                      | Н                               | H                                   | 7.56  | 5.93                                              | H-H<br>W                            |

| IBM System.<br>360 Basic<br>Model 44                        | 1.0                      | Н                               | S                                   | 7.63  | 5.1                                               | S⊶S¢<br>wa                          |

| IBM System<br>360 Model<br>44 with<br>high speed<br>General | 1.0                      | H                               | S                                   | 5.02  | 3.39                                              | Specinc:<br>ase<br>cons<br>nt       |

| Registers                                                   |                          |                                 |                                     |       |                                                   | tor<br>1.6                          |

| ICL 1902                                                    | 6.0                      | S                               | S                                   | 52.97 | 599.56                                            |                                     |

| ICL 1903                                                    | 2.0                      | S                               | S                                   | 17.96 | 253.17                                            | 190<br>190                          |

|                                                             |                          |                                 |                                     |       |                                                   | H/S<br>trac<br>off                  |

| · .                                                         |                          |                                 |                                     |       |                                                   | ava:<br>ble<br>with<br>MOVI         |

|                                                             |                          |                                 | •                                   |       |                                                   | inst<br>tior                        |

| ICL 1904                                                    | 2.0                      | S                               | H                                   | 14.50 | 37.79                                             | 1904<br>1905                        |

|                                                             |                          |                                 |                                     |       |                                                   | H/S<br>trad<br>off                  |

|                                                             |                          |                                 |                                     |       |                                                   | with<br>floa<br>ing<br>arit<br>meti |

| ICL 1905                                                    | 2.0                      | H                               | Н                                   | 14.50 | 8.97                                              |                                     |

| •                                                           |                          |                                 | •                                   |       |                                                   |                                     |

| ICL 1906 | 1.1 - 2.25 | H | H · | 9.09  | 1906-1907<br>CPUs are<br>identical<br>except<br>for float-<br>ing point<br>arithmetic |

|----------|------------|---|-----|-------|---------------------------------------------------------------------------------------|

| ICL 1907 | 1.1 - 2.25 | H | H   | 3.18  |                                                                                       |

| ICL 1909 | 6.0        | Н | ç   | 15.26 | -                                                                                     |

Table 2.3: Comparison of some word-oriented computer systems for commercial and scientific applications

From the results in the table, the following observations can be made: Comparison of IBM 7040 and IBM 7044 is given below:

- (i) The IBM 7044 is about 2.6 times faster for scientific computations and about 2.9 times faster for commercial workload. The main contribution to this increase in speed comes from the higher main memory speed of the IBM 7044 (it is 4 times faster). These machines are more suited for scientific computations. The main drawback of their instruction sets is the paucity of character handling instructions.

- (ii) The IBM System/360 Model 44 is also a machine suited for scientific computation, as advertised. This system is provided with fast hardware for floating

point arithmetic. However, the advertisement that this system is 'optimised for scientific computation' also refers to the fact that several of the excellent character handling instructions available with other models have been excluded in the instruction set of Model 44. Trade offs in speed available with faster registers are easily seen. As is evident, the speed increase by a factor of 1.6 in both scientific and commercial computation, is solely due to use of high speed General Registers.

(iii) ICL 1902, 1903 and 1904 computer systems are clearly meant for commercial workloads. Floating point arithmetic is done by software in these models and hence the anreally in speeds for the two types of workloads. ICL 1903 does not have storage-to-storage instructions. In all other aspects (except floating point operations), it is equivalent to ICL 1904 and 1905. Hence the difference between commercial computation speeds of these models and the other two. It is seen that ICL 1904 and ICL 1905 are equally powerful for commercial workload but ICL 1905 has hardware for floating point arithmetic. This is a good example of hardware-software trade offs available with the floating point feature. The same could be expected of the next pair in the family, the ICL 1906 and 1907 systems. Another surprising result is that even though ICL 1906 has faster core memory speed than ICL 1905, it is slower in scientific computations. The total percentage of floating point operations in the Arbuckle Mix is only 17.1. Even so, better floating point hardware of ICL 1905 offsets the higher core memory speed of ICL 1906 for this type of computation.

In all the above calculations, various instruction times, given in the introductory texts and programming manuals supplied by the manufacturer, have been used. Normally, these figures quoted by the manufacturer are optimistic instruction times. This is done in order to account for any local concurrency in the action of the CPU. In practice the effectiveness of these features depends on the nature of the user workload. This will be elaborated in the following paragraphs. A closer look at some of the components of a CPU, which provide the basis for local concurrency in its operation, is necessary.

Local concurrency is overlap in the execution of neighbouring instructions in an instruction stream. That is, one or more instructions are in the decode phase while one or more preceding instructions are in the operation phase concurrently.

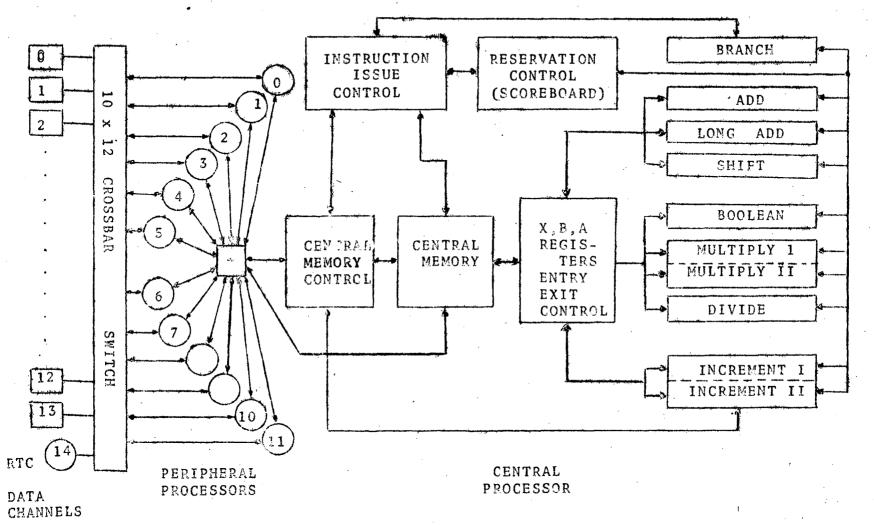

To make this possible, the CPU is designed as a set of functional hardware units as in the CDC 6600 computer system. These units each perform a micro-operation in the sequence of operations required to execute an instruction. Conventionally, in order to simplify the logical design of the CPU, these units are not available for processing succeeding instructions throughout the execution time of the current instruction. For better utilization of such hardware, the current practice is to release the units on completion of their operation; the released unit is reset or initialised immediately so as to make it available for the operation required by the next instruction, regardless of the completion of execution of the current instruction. Examples of functional hardware units are the fixed point arithmetic unit, the floating point arithmetic unit, the logical unit, the operation-code decoding unit and the effective address generation unit.

Parallel independent operation of these functional hardware units is possible only if enough information (instructions and operands) are available to them. There exists a need for buffering this information in a fast accessable store so as to bridge the CPU-speed main-memory-speed mismatch. Various techniques have been implemented; their design and performance have been studied by simulation techniques and are discussed in the next chapter. However, so long as the speed

mismatch exists, the number of registers in the CPU and extent of the data path between the main memory and the CPU determine the extent of local concurrency possible. The CDC 6600 CPU can process upto three instructions concurrently; these instructions are necessarily not interdependent, i.e. the outcome of any of these instructions does not depend on the outcomes of the preceding instructions. An even more powerful example of local concurrency in the CPU is Project Stretch, IBM 7030; in this sytem, upto eleven instructions can be in various stages of processing and any interdependence within these instructions is automatically taken care of by the instruction look ahead unit of the CPU.

Another point to be noted is the density of information retrieved per memory reference. With regard to instructions, this could mean the number of instructions packed into the width of the data path between the CPU and the main memory. Maximum density is achieved by provision of instructions of variable length; normally, instructions need either no memory reference or specification of one to two addresses for their execution. For operands, the density of information retrieved depends on the flexibility of the addressing scheme provided in the instruction format. The maximum density is related to the smallest addressable unit of main memory.

The reason for this elaborate digression on local concurrency features of the CPU is to bring out the inadequacy

40

÷,

of the simple instruction mix (representing any given application) in evaluating the speed of computation of the CPU. It is clear that a lot of information about the workload - other than the occurrence of types of instructions - is necessary to evaluate the performance of the CPU.

One way of dealing with differences in central processors and coping with difficulties like local concurrency is to compare the times required to perform specified taskscalled 'kernels'. These <u>tasks</u> are coded in the assembly language of the computer system and hence can utilize all the features of the computational facility offered. There is of course no standardisation either of the <u>tasks</u> to be performed or their magnitude. According to Calingaert [21] a kernel is "the central processor coding required to execute a task of the order of magnitude of calculating a social security tax, or inverting a matrix, or evaluating a polynomial". An attempt is made to have the problem coded with equal levels of sophistication by experienced programmers in assembly language.

Again, to represent actual working conditions, a fairly comprehensive set of kernels must be defined. The problem of assigning proper weights to these kernels in synthesising the workload is crucial in evaluating the computational

speed of the central processor by this method. An idea of the types of kernels defined and used so far has been given by Sharpe [19]. Examples are matrix multiplication, square root approximation of floating point numbers, field manipulation (control card scans, source statement scans), editing, field comparison, BCD arithmetic, character manipulation, polynomial evaluation etc. Elaborations on these kernels is given by Sharpe [19].

Kernels are much more general than instruction mixes as they make it possible to compare CPUs with entirely different characteristics. Even in the comparison of CPUs of a family of computers with the same instruction set, kernels are more powerful than instruction mixes as they give the actual distribution of types of instructions. Hence, it is possible to compute CPU times in the light of the actual local concurrency possible. Put in another way, the kernel approach in compari<sub>me</sub>. CPUs with identical instruction sets does not degenerate to instruction mix comparisons due to reasons outlined above (Sharpe has opined that the kernel approach degenerates to the instruction mix approach for the above case, an observation that is objected to here).

This approach has been very successfully used in the selection of computers for postal services in Britain [26].

Features like the 'stack' and associated operations can be included in evaluation of computation speed by this approach whereas this is not at all possible with the instruction mix technique. Stacks prove to be very useful in certain application. Stack oriented programming technique is explained by Dijkstra [27] and an implementation of such a feature in KDF9

is explained by Hassit [2].

Non local concurrency within a CPU is 'simultaneous' processing of instruction streams which are not necessarily interdependent. This is made possible by the interrupt feature of the CPU. In view of performance, the effort required to switch from one instruction stream to another and levels of priority in the interrupt feature, are the main interests.

As is well known, the CPU operates in two modes or is in one of two states. These are:

(i) the privileged mode or supervisor state and

(ii) the normal mode or the problem state.

In a general purpose computer system, the occurrence of an interrupt switches the CPU to the privileged mode. All computations needed to service an interrupt, constitute a part of the overhead incurred.