#### Inter PC Communication

Dissertation submitted to the Jawaharlal Nehru University

in partial fulfilment of the requirements for

the award of the Degree of

MASTER OF TECHNOLOGY

#### V. KISHAN

School of Computer and Systems Sciences

Jawaharlal Nehru University

New Delhi

January 1988

#### Inter PC Communication

Dissertation submitted to the Jawaharlal Nehru University

in partial fulfilment of the requirements for

the award of the Degree of

MASTER OF TECHNOLOGY

#### V. KISHAN

School of Computer and Systems Sciences

Jawaharlal Nehru University

New Delhi

January 1988

#### CERTIFICATE

This work, embodied in the dissertation titled,

#### INTER PC COMMUNICATION

has been carried out by Mr.V.Kishan ,bonafide student of school of computer and systems sciences, Jawaharlal Nehru University, New Delhi.

This work is original and has not been submitted for any degree or diploma in any other university or institute.

CMM

Dr.S.Balasundaram

Asst.Professor

School of Computer and Systems Sciences

Jawaharlal Nehru University

New Delhi

Prof Karmeshu

Dean, School of Computer and Systems Sciences Jawaharlal Nehru University

New Delhi

#### SYNOPSIS .

If an institute or organization has more than one computer system, it is very much essential that these computers to be interconnected, so that they can exchange information. My aim in this project is to -

Interconnect two PCs with RS232-C interface and then provide facilities for file transfer between the PCs and other utilities like mail and phone. The file transfer between the pcs is carried out in the background by implementing multitasking. Resource sharing is incorporated wherein a printer connected to one of the pcs can be accessed by the other PC as well.

The PC to PC connection can be improved with some more facilities and some more PCs can be connected  $^{ullet}$  to the existing two node network.

#### ACKNOWLEDGEMENTS

My sincere thanks are due to Dr A.K.Dua, Systems Manager, CMC Ltd, New Delhi who initiated me to this innovative project.

I 'am very much indebted to my guide, Dr.S.Balasundaram, Asst.Professor, who has been extreemly helpful and encouraging throughout the project, without which it would have been very difficult to complete the project.

Mr.Sanjiv Aggarwal, Systems Engineer, CMC Ltd, New Delhi played a very significant role by giving me timely and usefull suggestions and sparing his valuable time for discussions with me.

Mr.Katpalia of DCM data products gave very useful suggestions regarding the implementation of multitasking. I am thankful to him.

I express my heartfelt gratitude to Prof.K.K.Nambiar, former dean of our school, for providing the required facilities and for his unfailing interest he has shown in this project, without which it would not have materialized.

I am thankful to our dean Prof.Karmeshu,who has shown special interest in my work.

### CONTENTS

| 1.                               | Intro  | duction                                  | 1  |

|----------------------------------|--------|------------------------------------------|----|

| 2.                               | IBM P  | C and RS232-C Architecture               | .3 |

|                                  | 2.1    | 8088 Architecture                        | 3  |

|                                  | 2.2    | Interrupts and interrupt service routins | 8  |

|                                  | 2.3    | Serial asynchronous communication        | 13 |

|                                  | 2.4    | RS-232C serial data transfers            | 17 |

| з.                               | PC to  | PC communication                         | 18 |

|                                  | 3.1    | Introduction                             | 18 |

|                                  | 3.2    | UART intialization                       | 20 |

|                                  | 3.3    | Implementation                           | 22 |

|                                  |        | 3.3.1 The RESPC module                   | 23 |

|                                  |        | 3.3.2 The SYSINT module                  | 29 |

|                                  |        | 3.3.3 The TIME_INT module                | 31 |

|                                  | •      | 3.3.4 The PCNET module                   | 33 |

|                                  | ,      | 3.3.5 The FACILITY module                | 37 |

|                                  |        | 3.3.6 The PHONE facility                 | 48 |

|                                  |        | 3.3.7 The MAIL facility                  | 48 |

|                                  |        | 3.3.8 The file transfer utility          | 51 |

|                                  |        | 3.3.9 Resource sharing with DOS utility  | 51 |

| 4.                               | Instru | ictions for use                          | 54 |

| 5.                               | Future | e extensions and modifications           | 55 |

| Appendix A 8088 instruction set  |        |                                          |    |

| Appendix B Programming 8250 UART |        |                                          |    |

| Program listings                 |        |                                          |    |

#### INTRODUCTION

As computers have become smaller, cheaper and more numorous, people have become more and more interested in connecting them together to form networks and distributed systems. Advanced computer and communication technology has been the key to survival of a many institutions and organizations. The exciting tools and techniques of this high technology are used in high technology base, for arriving at general solutions and for applications support. These approaches to the implementation of computer metworks are revolutionizing communications, business systems and manufacturing and technology. When different computers can communicate with each other and are interconnected into a network, we have many advantages like —

- greater reliability

- sharing common resourses

- better support facilities

- faster response time

- internetworking capabilities

- flexibility in application programs and so on.

Most of the terminals that connect office desks to mainframes are dumb. In contrast, the personal computer is fast developing into an intelligent user-programmable terminal. It is a monotask but multi processor, low cost, high capacity device. There is a significant trend toward multifunction work station as opposed to single

function terminals. Interconnecting personal computers into a local area network and networking these with a main frame system offers many advantages.

#### MOTIVATION FOR THIS PROJECT :

We, at JNU have very good computing facilities. The systems include a VAX 11/780, HP1000 and six DCM TANDY1000 pcs. So far these computers are isolated and there is no way a user working on one system can look into his files on the other machine. My basic aim is to provide this facility. Since networking all these computers in not a task that can be completed with in a semester of six months, i started with a subset of it.

I want to connect all the pcs into a local area network. As a first step towards this, i wanted to interconnect two pcs through RS-232C, so that they can exchange information. This can be extended to interconnect all the pcs into a token ring network. By adding some more software, the pcs can also be connected to the VAX. Collision detection has to implemented when more than two pcs are interconnected. Ideally the master pc should be a PC/XT or a PC/AT.

#### II.IBM PC AND RS232-C ARCHITECTURE

The brain of the personal computer is the 8088 microprocessor. This chapter gives an introduction to the architecture and programming aspects of the INTEL 8088 microprocessor and it's communication aspects.

#### 2.1 8088 Architecture

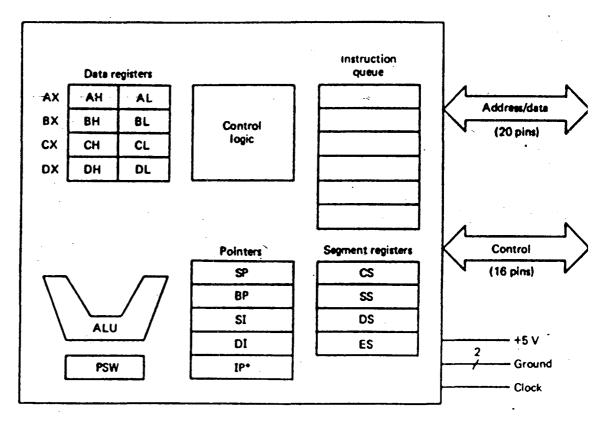

Fig 2.1 shows the internal architecture of 8088 microprocessor. The control unit and working registers are divided into three groups according to their functions. They are -

- i. The data group ,which is essentially the set of arithmetic registers,

- ii.The pointer group ,which includes base and index registers, but also contains the program counter and stack pointer,

- iii. The segment group which is a set of special purpose base registers.

All the registers are 16 bit wide.

The data group consists of AX,BX,CX and DX registers. These registers can be used to store both operands and results and each of them can be accessed as a whole,or lower and upper bytes can be accessed separately.

In addition to serving as arithmetic registers, the BX,CX and DX registers play special addressing, counting and I/O roles.

BX may be used as a base register in address

<sup>\*</sup>For the 8086 the program counter is called the instruction pointer (IP).

FIG 2.1 8088 BLOCK DIAGRAM

calculations.

CX is used as an implied counter by certain instructions.

DX is used to hold the I/O address during certain I/O operations.

The pointer and index group consists of the IP,SP,BP,SI and DI registers. The instruction pointer (IP) and SP registers are essentially the program counter and stack pointer registers, but the complete instruction and stack addresses are formed by adding the contents of these registers to the four bit left shifted contents of the code segment(CS) and stack segment(SS) registers. BP is a base register for accessing the stack and may be used with other registers and/or a displacement, that is a part of instruction. The SI and DI registers are for indexing. Although, they may be used by themselves, they are often used with the BX or BP registers and/or a displacement. Except for the IP, a pointer can be used to hold an operand, but must be accessed as a whole.

To provide flexible base addressing and indexing, a data address may be formed by adding together a combination of the BX or BP register contents, SI or DI register contents and a displacement. The result of such computation is called an effective address(EA) or offset. The final data address, however is determined by adding the EA to the four bit left shifted contents of the appropriate data segment, extra segment or stack segment registers. This

enables the proceesor to generate a 20 bit address .

The segment group consists of the CS,SS,DS and ES registers. The utilization of the segment registers essentially devides the memory space into overlapping segments,with each segment being 64k bytes long and beginning at a 16 byte paragraph boundary, i.e beginning at an address that is divisible by 16. So the contents of the segment register is the segment address and the segment address multiplied by 16 is the beginning physical segment address.

The advantages of using segment registers are to 1. Allow the memory capacity to be one magabyte even though the addresses associated with the individual instructions are only 16 bits wide.

- 2. Allow the instruction, data or the stack portion of a program to be more than 64k bytes long by using more than one code, data or stack segment.

- 3. Facilitate the use of separate memory areas for a program, it's data and the stack.

- 4. Permit a program and/or it's data to be put into different areas of memory each time the program is executed.

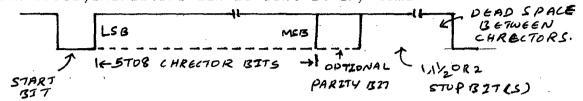

FLAGS: The 8088's Program status word(PSW) contains 16 bits, but seven of them are not used. Each bit in the PSW is called a flag. The flags are divided into the conditional flags, which reflect the result of the previous operation involving the ALU, and control flags which control the execution of special functions.

The flags are summarized below. The lower byte in

the PSW corresponds to the eight bit PSW in the 8085 and contains all of the condition flags, except the overflow flag(OF).

The condition flags are -

SF (sign flag) is set if the result is negative, reset if positive.

ZF (zero flag) is set if the result is zero and reset if the result is nonzero.

PF (parity flag) is set if the lower order eight bits of the result contain an even number of ones, otherwise it is cleared.

CF (carry flag) - an addition or subtraction causes this flag to be set if a carry in MSB or a borrow is needed.

AF (auxiliary carry flag) is set if there is a carry out of bit 3 during an addition or a borrow by bit 3 during a subtraction. This is used exclusively for BCD arithmetic.

OF (overflow flaq) is set if an overflow occurs.

DF (direction flag) - used by string manipulation instructions. If clear, the string is processed from it's beginning with the first element having the lowest address. Otherwise the string is processed from the high address towards the low address.

IF (interrupt enable flag) - If set, a certain type of interrupt (a maskable interrupt) can be recognized by the CPU, otherwise these interrupts are ignored.

TF (trap flag) if set, a trap is executed after the current instruction.

The 8088 provides various addressing modes, for details see Microcomputer Systems: The 8086/8088 family by YU-CHENG LIU and GLENN A.GIBSON. See appendix A for the instruction set of 8088.

#### 2.2. Interrupts and interrupt service routines

It is sometimes necessary to have a computer automatically execute one of a collection of special routines, whenever certain conditions exist within a program or the computer system. The action that prompts the execution of one of these routines is called an interrupt and the routine that is executed is called an interrupt service routine. There are two general classes of interrupts and associated routines. They are the interanl interrupts that are initiated by the state of the CPU or by an instruction and the external interrupts that are caused by a signal being sent to the CPU from elsewhere in the computer system. Typical internal interrupts are those caused by division by a zero or a special instruction like INT and typical external interrupts are caused by the need of an I/O device to be served by the CPU.

In general interrupts can be recognized in two ways.

a. By polling and b.Interrupt basis. In polling, the CPU regularly checks the I/O ports for any pending interrupts. The disadvantage with polling is that the CPU time will be

wasted, since the CPU has to regularly check the I/O devices. Not only that, data can be lost at the I/O port if there is considerable delay in successive pollings. In the other mode, i.e., interrupt basis the CPU recognizes the interrupt only when the I/O device sends an interrupt.

An interrupt service routine is similar procedure, in that it may be branched to from any other program and return branch is made to that program after interrupt service routine is executed. The interrupt service routine must be so written that, except for the lapse in time, the interrupted program will proceed just as if nothing had happened. This means that the PSW and the registers used by the routine must be saved and restored and the return be made to the instruction following the instruction executed before the interrupt. An interrupt service routine is unlike a procedure in that, instead of being linked to a particular program, it is sometimes put in a fixed place in memory. Because it is not linked to other. segments, it can use only common areas that are absolutely located to communicate with other programs. Because some kinds of interrupts are initiated by external events, they occour at random points in the interrupted program. For such interrupts no parameter addresses can be passed to the interrupt routine.Instead, data communication can be made through variables that are directly accessible routines.

Regardless of the type of the interrupt, the

action that results from an interrupt are the same and are known as the interrupt sequense. Some kind of interrupts are controlled by the IF and TF flags and in those cases, these flags must be properly set or else the interrupt action is blocked. If the conditions for an interrupt are met and the necessary flags are set, the instruction that is currently executing is completed and the interrupt sequence proceeds by pushing the current contents of the PSW,CS and IP on to the stack, inputting the new contents of IP and CS from a double word whose address is determined by the type of interrupt and clearing the IF and TF flags. The new contents of the IP and CS determine the beginning address of interrupt service routine to be executed. After the interrupt has been executed, the return is made to the interrupted program by an instruction called IRET which pops the IP,CS and PSW from the stack.

The double word containing the new contents of IP and CS is called the interrupt pointer. Each interrupt type will be given a number between 0 and 255 inclusive and the address of the interrupt pointer is found by multiplying the type by 4. These addresses are loaded by the operating system when the system is booted.

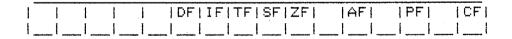

I/O operations that take place between I/O devices and CPU on an interrupt basis are called interrupt I/O.Since there is only one interrupt input to an 8088,in order to support more than one device, programmable interrupt priority management circuit (8259) is connected to INTR and INTA pins of 8088.See Fig 2.2 for a block diagram

<sup>\*</sup>AO \* 0 for addressing the first word (ICW1) and 1 for addressing the succeeding words.

# FIG 2.2. 8259 INTERRUPT PRIORITY MANAGEMENT BLOCK DIAGRAM

<sup>&</sup>lt;sup>2</sup> AO = 1 for addressing the first word and 0 for addressing the succeeding words.

<sup>&</sup>lt;sup>3</sup> Bits correspond to IR inputs, Bit = 1 means IR is masked and Bit = 0 means it is not masked.

<sup>4</sup>tf 8259A is a master, Bit = 1 indicates that the corresponding IR input is connected to a slave. For a slave, bits 3-7 are 0 and bits 0-2 identify the slave.

of 8259 interrupt controller.I/O devices are connected to the different levels of priority management circuit.Each level is assigned a unique interrupt vector. When an interrupt comes from a device on a particular level, priority management circuit checks for the priority.If any higher priority interrupt is in progress ,it keeps it in pending, otherwise it interrupts the CPU on behalf of the I/O device and sends the interrupt vector number which enables the CPU to respond to the interrupt.

interrupt priority management contains the logic needed to assign priorities to incoming requests. For example, the highest priority could be given to IRO, the next priority to IR1 and so on. When interrupt request is recognized by the priority logic as having the highest priority, then the three least significant bits of the type register are set to the number of the request line, a bit is set in the inservice register and interrupt is sent to the CPU. If IF flag is set then the CPU returns an acknowledgement signal and the management circuit sends the CPU the type. All the requests having priority are blocked untill the bit in the inservice register is cleared, an action which is normally done by routine.Therefore when IF is reenabled STI instruction, higher priority requests may interrupt currently executing routine, but the lower priority requests will be blocked by the priority logic until the bit that was set in the in service register is cleared. This allows the

lower priority interrupts to proceed. The priority management circuit is programmable.

For details of programming the 8259 refer INTEL manual.

In addition to the built in priority, a one byte mask register is provided to allow the masking of individual requests. Bit n in this register is for masking IRn.

#### 2.3 Serial asynchronous communication

For two computers to exchange information, there should be proper interface between them. This is provided through a communication link, which facilitates the data transfer.

Within the computer, data is transferred in parallel, because that is the fastest way to do it. For transferring data over long distances, however parallel data transfer requires too many wires, which is not feasible when the computers are located far apart. Therefore data to be sent to long distances is usually converted from parallel form to serial form, so it can be sent on a single wire or a pair of wires. Serial data received from a distant source is converted to parallel form, so that it can be easily transferred to the computer bus.

Serial data can be sent synchronously or asynchronously. For synchronous transmission, data is sent in blocks at a constant rate. The start and end of block are identified with specific bytes or bit patterns. For asynchronous transmission, each data character has a bit

which identifies it's start and one or two bits which identifies it's end. Since each character is individually identified, characters can be sent at any time.

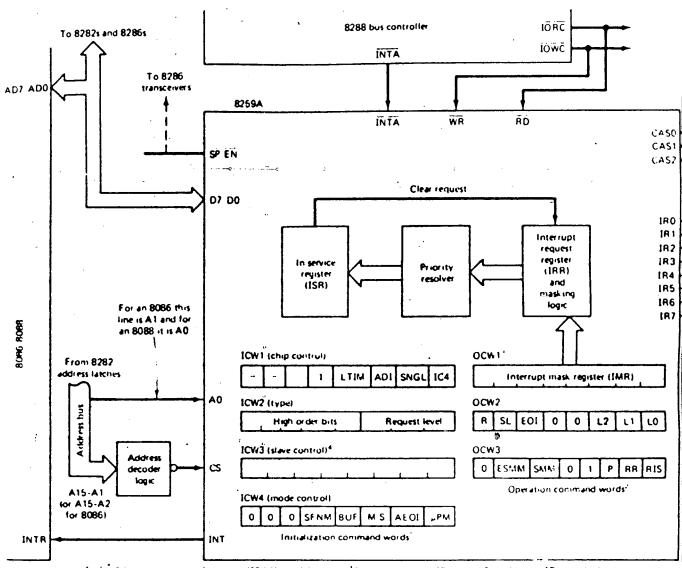

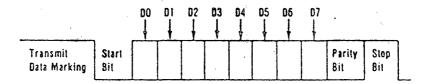

Fiq 2.3 Asynchronous communication format

Fig 2.3 shows the bit format often used for transmitting asynchronous data.When no data is being sent, the single line is in a constant high or state. The beginning of a data character is indicated by line going low for one bit time. This bit is called a bit. The data bits are then sent out on the line one after other.The significant bit the least is first.Depending on the system,the data word may consist 5,6,7 or 8 bits. Following the data bits, a parity used to check for the errors in the received data. Some systems do not insert or look for a parity bit. After the data bits and parity bit ,the signal line is returned at least one bit time to identify the end character. This always high bit, is referred to as stop bit.Some systems use 2 stop bits.

The term baud rate is used to indicate the rate at which serial data is transferred. Commonly used baud rates are 110,300,1200,2400,4800,9600 and 19200.

To interface a computer with serial data lines, the data must be converted to and from serial form. A parrallel in, serial out shift register and a serial

in,parallel out shift register can be used to do this. A hand shaking circuitry is needed to ensure that the transmitter does not send data faster than it can be read in by the receiving system. There are available several programmable LSI devices which contain most of the circuitry needed for serial communication. A device such as the INS 8250 which can do asynchronous communication is referred to as a Universal Asynchronous Receiver Transmitter or UART.

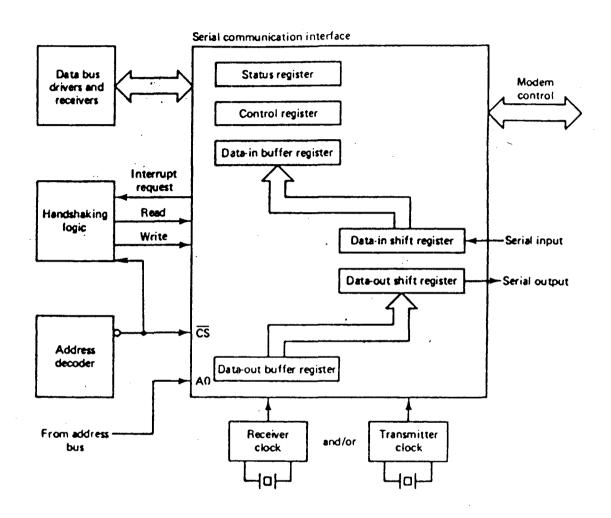

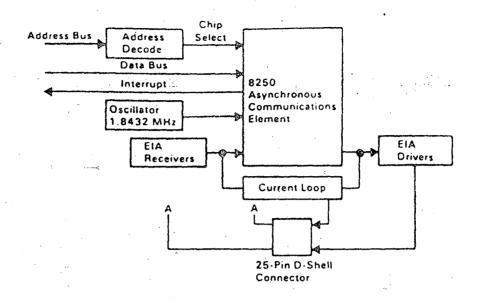

Fig 2.4 shows the block diagram of 8250. status register would contain error and other information concerning the state of the current transmission, and the control register is for holding the information that determines the operating mode of the interface. The data buffer is paired with data in shift reqister.During an input operation, the bits are brought into the shift register one at a time and after a character has been received, the information is transferred to the data iπ buffer register, where it waits to be taken by the CPU. Similarly the data out buffer is associated with a parallel output shift register.An output is performed by sending data to the data out buffer, transferring it to the shift register and then shifting it to the serial output line.

Although there are several ways in which the four port registers can be addressed, it has been assumed that the status register can only be read from and control register can only be written into. Therefore an active signal on the read line would indicate either the status or data in buffer

FIG 2.4

8250 VART BLOCK DIAGRAM

register. The interface has separate lines for sending and receiving information. So it can be used as a full duplex channel.

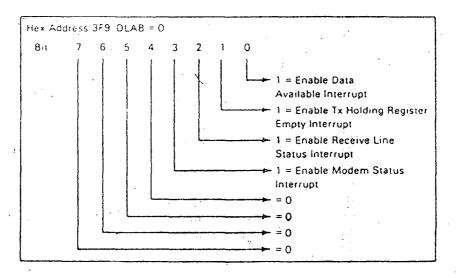

The information can be read from data\_in register either by polling or on an interrupt basis.In our implementation, the characters are received on an interrupt basis.Accordingly the 8250 is programmed to interrupt whenever there is a character in data\_in register.It is also programmed to the appropriate baud rate, number of stop bits, number of data bits, and the parity.

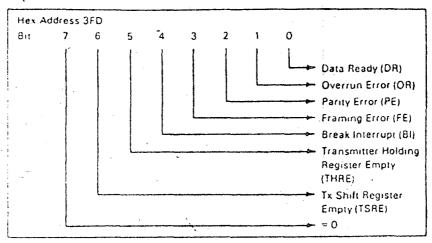

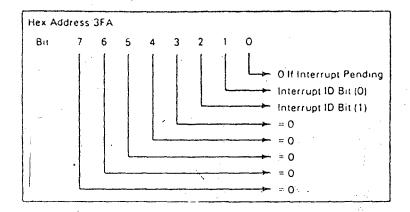

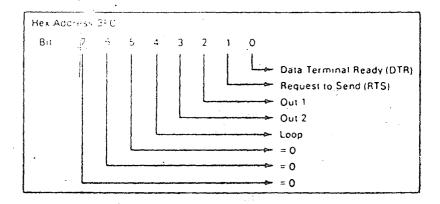

For details of programming the 8250, see appendix B.

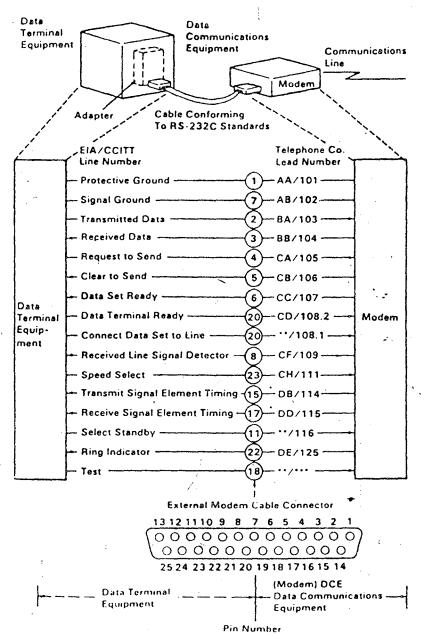

#### 2.4 RS-232C serial data transfer standards

Modems and other devices used to send serial data referred to as data communication are often equipment(DCE). The terminals or computers that are sending or receiving the data are referred as data terminal equipment(DTE). In response to the need for signal and hand shake standards between DCE and DTE the Electronics Industries Association (EIA) developed EIA standard RS-232C. This standard describes the configuration and function of 25 singnal and handshake pins for serial data transfer. It also describes the voltage level, impedence level, rise and fall times, maximum bit rate and maximum capacitance for these signal lines.RS-232C specifies 25 signal pins and specifies that the DTE connector should be a male and the DCE connector should be a female. A specific connector is not given, but the most commonly used connectors are the DB25-P

male and the DB25-S female. It is important to note the order in which the pins are numbered. See appendix B for RS-232C pin configuration.

The voltage levels for all RS-232C signals are as follows-A logic high or mark is a voltage between -3V and -15V under load. A logic low is a voltage between +3V and +15V under load. Voltages such as +/-12V are commonly used.

#### III . PC TO PC COMMUNICATION

#### 3.1 INTRODUCTION

For a terminal to communicate with a nearby computer, a simple RS-232C connection is sufficient. If the computer is distant, then a modem is required.

As another example of computer communication, suppose that we have several computers in one building or a complex of buildings, that need to communicate with each other. What is needed in this case is a high speed network, commonly called a local area network or LAN, connecting the computers together. In this part of the project, we are connecting two PCs via RS-232C, which will communicate at a baud rate of 9600. Since only two PCs are connected, no bus arbitration is required, However if more PCs are connected, then collisions have to be taken care of.

The facilities provided in this project are -

- a. File transfer between the pcs .

- b. Other utilities like mail and phone.

- c. Resource sharing.

The file transfer utility runs in the background. When a request for file transfer is made from pcl to pc2, a resident program on pc2 responds to the request and transfers the file in background. The user can continue his session as usual, and for the larger part, is unaware of

the file transfer. A printer connected to one of the PCs can be accessed by both the PCs.

Our aim in this work is to get the maximum throughput of the pcs and share the resourses like printer. When we are using RS-232C, the data transfer rate is always slow.RS-232C can support only upto 9600 baud rate, while the CPU execution speed is much higher. It has to wait till each byte is transferred. Not only this, we are keeping the user idle. A user requsting for a file can wait, but it is not reasonable to keep a file sender idle. To overcome this problem, we are doing the serving job in the background.

When there is a request from pc1, the process residing in pc2 is initiated and requests the user for his permission for the file transfer. If the request is granted, it continues the job, otherwise simply returns.

#### LANGUAGES CHOSEN

For writing interrupt service routines and adjusting the interrupt vectors, assembly language is the natural choice and we chose the same for our RESPC program.

The rest of the module is developed in TURBO pascal.Pascal, as such is a good procedural language and it is much easier to debug a program written in pascal.Compiling and debugging with TURBO Pascal is very easy because of it's speed and inbuilt editor.TURBO also provides excellent and very useful features like interface to assembly language programs, executing MSDOS interrupt service routines, windowing, direct memory access, direct port

addressing, efficient file handling and enabling and disabling I/O errors.

The assembly language interface is used iπ calling GETKEY and GETBUFF assembly functions. Many of procedures like POSCUR and 90 on utilize the software interrupt service routine execution facility.Windowing has æ direct usaqe with modifications for cursor positioning. Direct port addressing capability is utilized in addressing the 8250 communication port.

#### 3.2 UART INTIALIZATION

The theory and programming aspects of UART were discussed in chapter2. The PC has two communication ports and COM2.Each of them сап be independently programmed.For PC to PC communication,COM1 is used.The interrupt output of this device is connected to the IR4 interrupt of the 8259A priority interrupt controller in the PC mother board. The 8259A itself is mostly initialized BIOS when the system is booted. However, since the UART connected to IR4 of the 8259A,that input has to unmasked. To do this, the current contents of the 8259A interrupt mask register are read in from address 21H. The bit corresponding to IR4 (bit 4) is then ANDed with a unmask the interrupt and the result put back in reqister.

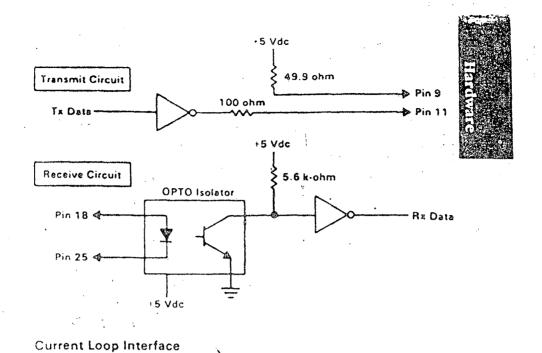

In this communication, only four wires are used (See Fig4.1). RXD (Receive Data), TXD (Transmit Data),

protective ground and signal ground; and 8250 is programmed accordingly.

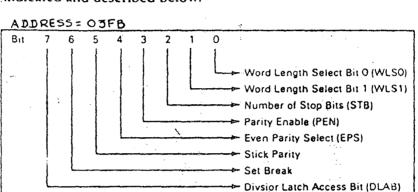

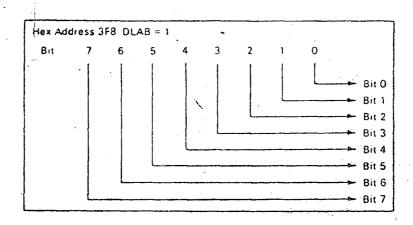

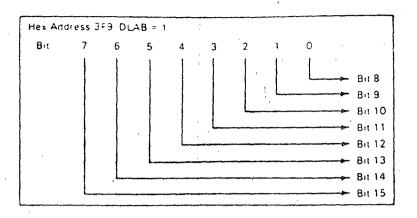

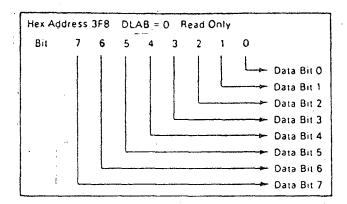

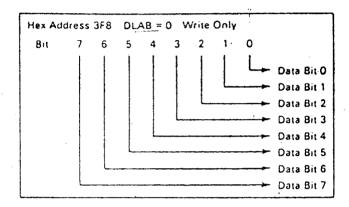

First the divisor latch register is programmed for the appropriate baud rate. To program the baud rate, the devisor latch address bit (DLAB) of line control register has to be set. So 80H is output to line control register.

Next, the divisor latch register 03F8H and 03F9H are programmed with the appropriate baud rate. For a baud rate of 9600, the values to be output are 00 to 03F9H and 0C to 03F8H. Since the communication parameters can be changed with in the session using the setup option, this baud rate is programmable and can be changed at any time.

Next, the line control register is programmed with the default parameters. For our communication, the parameters are 8 bit data, one stop bit and no parity. Hence 03 is output to the line control register. Like baud the line control register. Like baud

Since characters are received on an interrupt enable data available interrupt bit (bit 0) in enable register is set. So 01 is output to enable register.

interrupt enable register.

In this implementation, characters are received on an interrupt basis and buffered. These characters are later read from another program and processed. Let us consider a simple program where characters are received by polling the 8250 and displayed, and input from the keyboard is sent to another PC.

Initialize 8250

repeat

if keypressed, then read key and send it

if UART has a character, then read the

character and display it

forever.

The above program works well at 300bd or 600bd. However for a baud rate of 1200 and above, the first character of each line of characters received from the host will be lost. After a carriage return is sent to the CRT, the display on the screen is scrolled up one line. Not only this, the input from the keyboard has to be processed and the received characters have to processed for escape and control sequences, which takes considerable time. To avoid loss of characters during this time, the characters are received on an interrupt basis and stored in a circular buffer.

#### 3.3 IMPLEMENTATION:

This package consists of assembly programs and pascal programs, in which pascal programs are loaded and executed using assembly routines and assembly programs are called from pascal programs.

These programs are -

- 1. RESPC.ASM

- 2. PCNET.ASM

- 3. FACILITY.PAS

- 4. PHONE.PAS

- 5. MAIL.PAS

- 6. ASKFILE.PAS

- 7. DOS.PAS

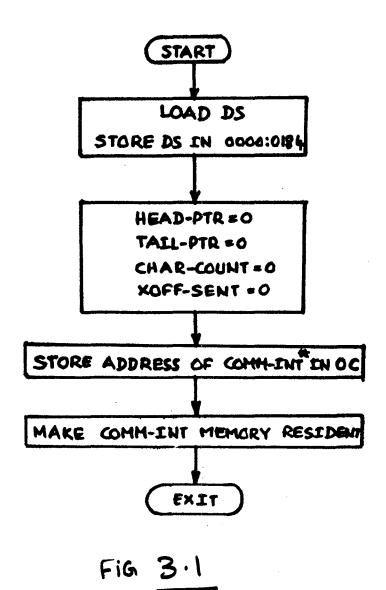

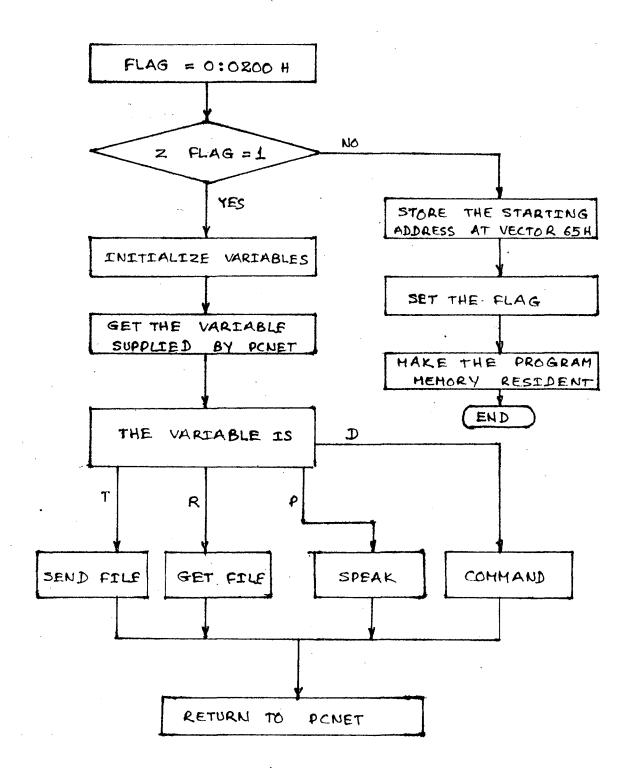

#### 3.3.1 RESPC: -

See Fig 3.1 for a flowchart of RESPC. This program is written in assembly language. It stores the characters in a circular buffer and another function GETBUFF (which is in another module) reads characters from this buffer. Since both these functions share certain parameters, there should be a way to access these common parameters. In this implementation, the Data Segment of RESPC is stored in 0000:0184H. GETBUFF later loads the DS with the data in 0000:0184H and accesses different parameters as offsets with in the data segment.

Since communication port is connected to IR4 of 8259A, the 8259A will send interrupt vector OC to the processor. So the starting address of the communication interrupt service routine is stored at vector 60H, using DOS function call 25H, later it will be stored at OC by a routine TEMPCOM .

The communication interrupt service routine,which is resident all the time in memory, receives characters from PC2 and stores them in circular buffer. The flow chart is given in fig 3.2

Since the interrupt can occour at any time, it is important to save the DS register and load the DS with DATA-HERE.

The buffer used here here is a circular buffer. One

# RESPC

## COMM-INT ENABLE INTERRUPTS SAVE AXBX, CX, DX, DI, DS LOAD DS WITH DATA SEGMENT OF RESIDEM read from Port OBF8 Inter INCREMENT TAIL-PTR YES TAIL-PTR = 1000 TAIL-PTR=0 HEAD-PTR YES TAEL-PTR NO STORE AL IN QUEUF POINTED BY TAIL-PTR INCREMENT CHAR-COUNT YES CHAR- COUNT <900 SEND XOFF TO VAX SET XOFF-SENT FLAG END OF INTERRUPT TO 8250 RESTORE REGS (RETURN) F16 3.2

pointer called the tail-pointer is used to keep track of where the next byte is written into buffer. Another pointer called the head-pointer is used to keep track of where the next character is to be read from the buffer. The buffer is circular because, when the tail-ptr reads the highest location in the memory space set aside for the buffer, it is wrapped around to the beginning of the buffer again. The head-ptr follows the tail-ptr around the circle as characters are read from the buffer. The checks are made on the tail-ptr before a character is written into buffer.

First the tal-ptr is brought into a register and incremented. This incremented value is then compared with the maximum number of bytes the buffer can load. If the values are equal, the pointer is at the highest address in the buffer. So the register is reset to zero, after current character is put into the buffer. The value will be loaded into the tail-ptr to wrap around to the lowest address in the buffer.

Secondly,a check is made to see if the incremented value of the tail-ptr is equal to the head-ptr. If the two are equal, it means that the current byte can be written, but for the next byte the buffer would be full. If this happens, an XOFF character is sent to PC2 to stop it from sending more characters and the xoff-sent flag is set. But. some characters may be sent by PC2 before we send XOFF. To avoaid this, every time a character is stored in buffer, a variable char-count is incremented. This char-count

is compared with 950 and if they are equal, an XOFF is sent and xoff-sent flag is set. This way the host is restrained from sending more characters before the buffer gets filled up.

The other procedure which reads characters from this buffer(GETBUFF) checks the xoff-sent flag after every read. If this flag is set, it checks the char-count to see if there is enough space in the buffer. If the char-count is less than 750, it sends an XON and resets xoff-sent flag. This assures that there is a buffer space of 250 characters and RESPC can ressume buffering.

Finally before returning, an end of interrupt command must be sent to the 8259A to reset bit4 of the interrupt mask register.

PCNET is an assembly program, consisting of SYSINT, TIME\_INT and TEMPCOM interrupt routines. Before proceeding to describe these routines, it should be born in mind that MSDOS is a single user operating system and it's code is not reentrant. In our program, the file transfer is carried in multitasking. SYSINT and TIME\_INT serve this purpose.

For all I/O functions and certain special functions, every program has to request the operating system, with the proper parameters. The operating system does the specified task and gives control back to the called process. IBM pc provides some firmware routines for certain

basic functions and MSDOS provides variety of routines under interupt 21H with different function calls.(See DOS technical reference manual for detailes). Since MSDOS is a single user operating system, we can run only one process at a time and only one function request is made at a time. The process requests for system services one after the other. Since MSDOS routines are not reentrant, in the multitasking, when a process enters the system routine, other process should not be allowed to enter. If this is allowed the system will crash. We can implement multitasking, by executing each process till it's time slice expires. This works very well if both processes are not requesting for system services at the same time.

But imagine a case, where multitasking is implemented and a process called a system function ,and it's time slice is over when it is halfway through in the system call. If control is passed on to the other process, and if that process also requests for the same function, there is no way MSDOS can know that the request has come from the second process and it is in the way of serving it. Hence the register variables of the first process will be reinitialized ,which will lead to system crash. One solution to this is to execute the process, though it's time slice has expired. But this may lead to another problem, where the system routine may be indefinitely waiting for the input.For example it may indefinitely wait for an input from keyboard. The user may take his own time in giving the input.During this time,the process is simply waiting for the

input from the keyboard and the second process can not be served. Since MSDOD is serving one process, we should keep the other process's request in pending. Another solution to this problem is not to allow MSDOS to respond to keyboard I/O until a key has been pressed. This method is implemented in the following SYSINT routine.

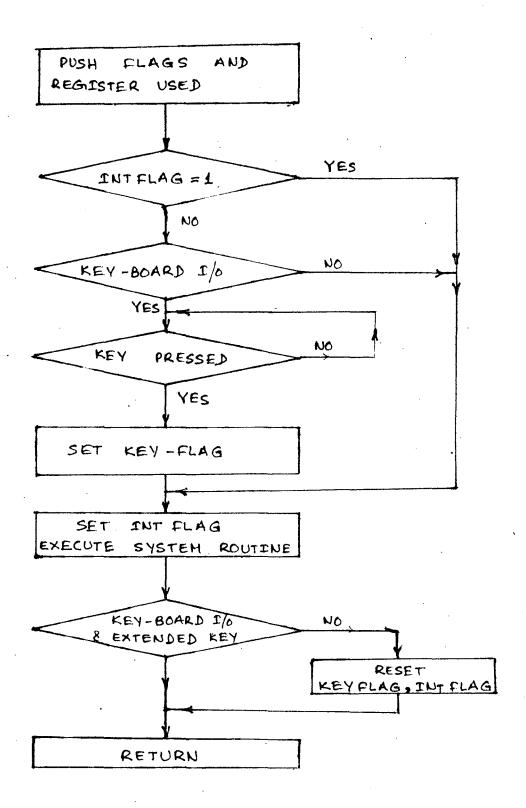

3.3.2 SYSINT: When a system call is made by a process, it puts the appropriate values into the registers and executes the corresponding interrupt. Then control branches to the appropriate address and the routine is executed. When we run PCNET, it takes the address of the actual system routine and places it in vector 64H. It stores the starting address of SYSINT at vector 21H. So whenever a system call is made with vector 21h. The control is retained by SYSINT.

This SYSINT checks the int flag. If it is set, it gives control to the actual system routine. This is necessary because, when a process reads a key through MSDOS, it returns the ASCII value in AL register. If the key is an extended key, AL contains zero and another call must be made to get the extended code. When this happens, the next request must be served to the same process. For this, SYSINT sets the intflag, when the process is leaving the SYSINT in this particular case.

In the next step SYSINT checks whether the request is for keyboard I/O.If it is ,it simply loops until a key or keys are pressed. Then it sets the key flag and the int flag and gives control to the system routine. If

FIG 3.3

the request is not for keyboard I/O, it simply gives control to the system routine. Since it is looping for a keyboard input in SYSINT, TIME\_INT can give control to the other process. This int flag serves as an indicator to the TIME\_INT that a process is getting system service from MSDOS.

After executing the system service routine, control is returned to SYS\_INT.Then it resets the intflag.If the returned value is that of an extended key, then it sets the int flag , resets the keyflag and control is returned to the requested process. The flowchart is given in Fig 3.3

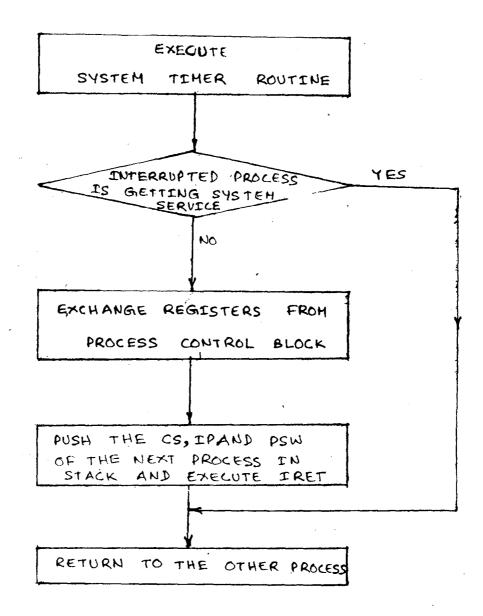

3.3.3 TIME\_INT : IBM PC has 8253-5 timer chip,which has three timers in it. One is connected to the CPU through 8259 interrupt priority controller, the second one is connected to DMA and the third is connected to the speaker. When the system is booted, MSDOS programs the first timer to interrupt the processor periodically, so that the timer routine does the time keeping. Timer has the highest priority interrupt. It IRO of the 8259 interrupt priority connected to controller. implementation, Multitasking Iπ our accomplished, using this timer. Whenever there is a timer interrupt, control is retained by our TIME\_INT routine. This routine first does the system time keeping, then it pops the instruction pointer code segment and PSW of the interrupted process from the stack. It checks whether the interrupted process is getting served by MSDOS by checking the intflag code segment of the interrupted process. If the the intflag is set or the code segment is equal to the segment

# TIME\_INT

FIG 3.4

the MSDOS system routine, it restores the stack and is returned back to the interupted control process.Otherwise, it stores all registers the control block and loads the registers with the values of the next process to be served, from the process control block of the other process .The PSW.CS and IP of the process to given control are pushed onto the stack and control is given back to that process by executing IRET instruction. flowchart is given in Fig 3.4

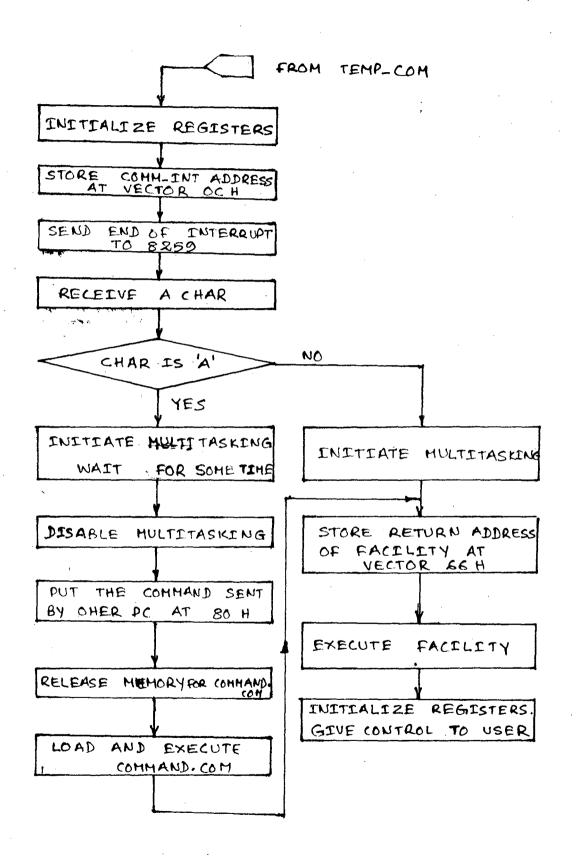

3.3.4 PCNET : This program initializes the 8250 such that, whenever it receives a character, it should interrupt the processor. It's interrupt level .on 8259 priority controller is IR4 and it's vector is OCh. PCNET stores address of the TEMPCOM interrupt service routine at OCH and 67H. This routine stores all the registers of the interrupted process, masks IR4 bit of the 8259 priority controller, so that another interupt is not recognized during the execution of this routine. Whenever there is an interrupt from 8250, it reads the characters from UART and checks if the caharacter is an escape character.If it is then it gives control to a process, where it checks for the request and serves it. If the received character is not an escape character, then TEMPCOM unkmasks IR4, sends an end of interrupt to 8259 and calls the disable function. This disable function places the starting address of the TEMPCOM at vector OCh and loads registers of the interrupted process from the process control block and gives control to it.

FIG 3.5 (CONTD)

FIG 3.5

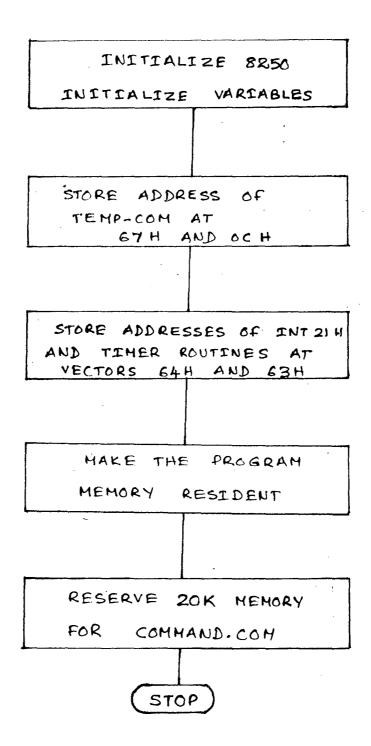

PCNET initializes 8250 by calling INIT subroutine for communication parameters of 9600 baud rate,8 bits,no parity and one stop bit and to generate interrupt, whenever a character is recieved. Then it loads the starting address of TEMPCOM at 0Ch and 67H, stores the addresses of the original timer and interrupt 21H service routines in 63H and 64H respectively, then stores the SYSINT address at vector 21H and makes the whole program memory resident by reserving another 20k of memory space.

When TEMPCOM gives control to PCNET after receiving an escape character, it initializes all the registers to execute this process and then copies COMM\_INT address from 60H to OCH. It sends a character 'C' to the other computer so that it can goahead. If the received character is other than 'A', it stores the address of the TIME\_INT routine at vector O8H and initializes multitasking. It then stores the return address of the pascal program at vector 66H and calls the pascal program FACILITY for further service.

If a user on one pc wants to run a command on the other pc,he will send an escape character ,followed by the character 'A'.To execute MSDOS commands,we should release around 17k of memory allocated to the current process to load a copy of COMMAND.COM into this memory.Then place the command string at offset 80H with the string length as the first byte and a carriage return as the string terminator .Then make the DS:DX to point to the string COMMAND.COM and make ES:BX point to the parameter block and

load AL with zero, AH with 4BH, save SS and SP registers in an area other than stack and execute interrupt 21H, which loads and excutes COMMAND.COM. This COMMAND.COM picks up the command stored at offset 80H and executes it.

On return from the executed command, most of the registers have been changed, including SS and SP. These registers have to be restored.

If the received character is 'A', it stores the TIME\_INT address at O8H, waits for some time and restores the original timer routine at OCH. Then it reads the command sent by the other user and places it in 80H and executes the command as explained above. Then it calls the module FACILITY, by placing the character 'D' in variable TRAY. The flowchart is given in Fig 3.5.

3.3.5 FACILITY: This program, written in pascal consists of external and internal procedures and functions. All external procedures and functions are coded in assebmly. Let us see how assembly programs are called from Turbo pascal and how parameters are passed.

When an assembly routine is to be called from a pascal program as a procedure/function, it should be defined as external procedure/function in the pascal program. The assembly program has to be separately assembled, linked and converted to binary form by using EXE2BIN utility.

Let us consider a pasçal program and an assembly program.

Pascal program

```

program pascal_assembly_interface;

function decr(var

integer)

integer;

external 'decr.bin';

var i,j : integer;

begin

i := 1;

j := decr(i);

write('i = ',i);

end.

Assembly program

; function decr(var n : integer); integer;

dear proc

near

PUSH

BP

MOV

.BP,SP

LES

DI,[BP+4]

AX,ES:[DI]

MOV

DEC

ΑX

MOV

ES:[DI],AX

POP

BP

6

RET

endp

```

where i is a variable in pascal initialized to 1. The assembly function DECR is called with the parameter i. The function takes the variable i, decriments it and returns the decrimented value. The pascal program then prints this returned value.

Let us see how the parameters are passed.Turbo Pascal passes parameters through stack.

At entry, the stack pointer points to the stacked return address of the caller to this routine. The higher address (sp+2) contains the address of the parameter passed by the caller. To access the parameter, we use BP register. Since this BP register would have been used in calling program,we must save BP as the first step in assembly program.In principle,all the registers that are being used in the assembly routine have to be saved, and then restored when returning control to the caller. Then the current stack pointer is assigned to BP. Both SP and BP the value of the saved BP register. The returnaddress address and the BP reqister values are each of two bytes, hence the parameter is found on the stack at location [BP+4]. The parameter is taken from this area, incremented and put back at the same location. BP register is restored and control is returned to the caller by executing RET. RET pops only the return address from the stack. we mustalso pop the paremeter, we shold use RET 6.

The following external procedures are used -

GETKEY: This function checks, if there is any input from the keyboard and returns the data if any, to the called program. The flow chart is given in Fig 3.6.

# GETKEY START SAVE BP BP - SP AH -- 01 INT 16 SET ZERO FLAG RESET AH -- 00 INT 16 ES:[DI] - AX RESTORE BP (RETURN)

Fig 3.6

CHECK IF KEY IS PRESSED

READ THE PRESSED KEY INTO AL

PUT THE KEY INTO EXTERNAL VARIABLE INT 16H BIOS routine provides different functions, depending on the value loaded in reg AH. AH=0 returns the code for a pressed key in AL. AH=1 returns the zero flag=0 if a key has been pressed. INT 16 is called with AH=1. If zflag is set, there is no input from the keyboard and execution returns to the caller. If the zflag is 0, the keyboard input is read into AL and the value returned.

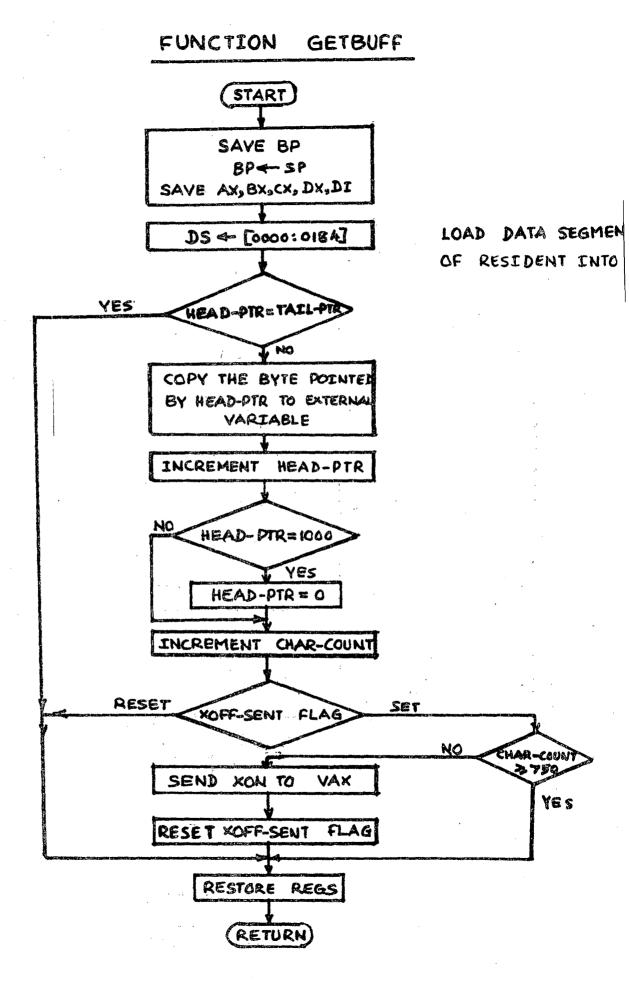

GETBUFF: This function checks if there is date in the circular buffer and returns the data, if there is any. The flow chart is given in Fig 3.7

All the registers are saved. The contents of [0000:0184] are loaded into DS, so that the variables of RESPC are accessible here. Once DS points to the data segment, the variables within the date segment are accessible as off sets using the registers BX and DI.

By comparing the head and the tail pointers, a check is made to see if there are any characters in the buffer. If not, the execution is returned to the caller. If a character is available in the buffer, it is read and the head pointer updated to point to the next available character. If the pointer is at the top of the space allocated for the buffer, the pointer is wrapped around to the start of the buffer. The read character is then passed on to the external variable. As discussed earlier, this function also checks the xoff\_sent flag and sends an XON if there is enough space in the buffer.

INTPAS: This routine stores the starting address of FACILITY at address 65H and makes the whole program memory resident and gives control to MSDOS.

RETURN: After the FACILITY program is called and executed from PCNET, this RETURN procedure takes the return address stored at vector 66H and gives control to PCNET.

NOSWAP: This procedure disables multitasking by placing the address of the MSDOS timer routine at vector 08H.

The additional procedures are -

FINDCUR: Finds the position of the cursor by loading 03 into AH, 00 into BX and executing interrupt 10H. The column number is contained in DL and the row number in DH. Row number varies from 0 to 23 and column number varies from 0 to 79 in PC, while they vary from 1 to 24 and 1 to 80 respectively in normal use so a 1 is added to the row and column numbers determined above.

POSCUR: Positions the cursor at the given row and column, by loading 02 in AH,00 into BX, rownumber-1 in DH, column number-1 in DL and executing interrupt 10H.A one is subtracted because of the same arguement as above.

DISPLAY: This Is used in displaying a character with a given attribute. When characters are to be displayed in a mode other than normal, the attribute byte is set and this procedure is called to display the character in the required

FIG 3.7

attribute.For carriage return, line feed and tab, the characters are displayed as they are. For the rest, the character is loaded in AL, 09 into AH, the attribute into BL, the number of characters into CL and interrupt 10H is executed. The cursor is moved to the next column.

SET\_DISPLAY: Displays a given string with a given attribute. It repeatedly calls the above procedure for each character of the string.

GETCHAR: In some cases it is necessary to wait till a character is received. This procedure waits till a character is received by repeatedly calling GETBUFF.

SEND: Sends an integer to the host. It reads the line status register of COM1 and checks if bits 5 and 6 corresponding to transmitter holding register empty and transmitter shift register empty are set. If they are set, then the data is sent to the output port [03F8].

READFILENAME: Reads the filename sent by the other user into the string variable called filename. If it is unsuccessfull in reading the filename, it sets fflag.

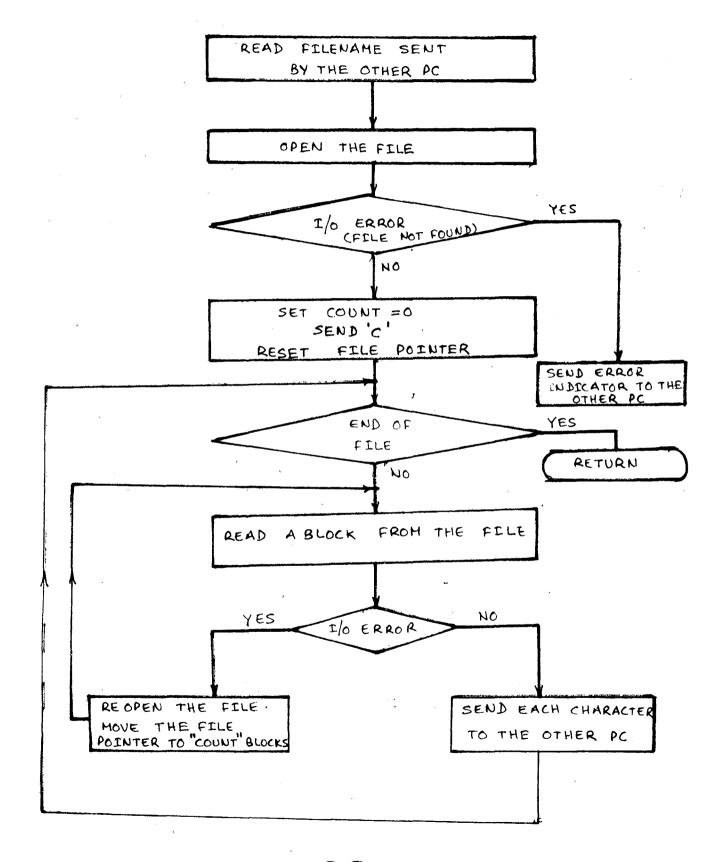

SENDFILE: This is the actual procedure which runs in the multitasking mode. It reads data from the required file and sends it to the other pc. Data is read from the file in blocks due to the following reason. When SENDFILE runs in the background and the user runs the directory command in the foreground, MSDOS flushes all it's file discriptors in the

# SENDFILE

FIG 3.8

memory and hence the file handle of the current file used in the background job will be lost and there will be I/O error. To overcome this problem, this program reads the file in blocks and keeps a count of the number of blocks read. If there is any error in reading the file, it reopens the file and positions the file pointer at the next block to be read.

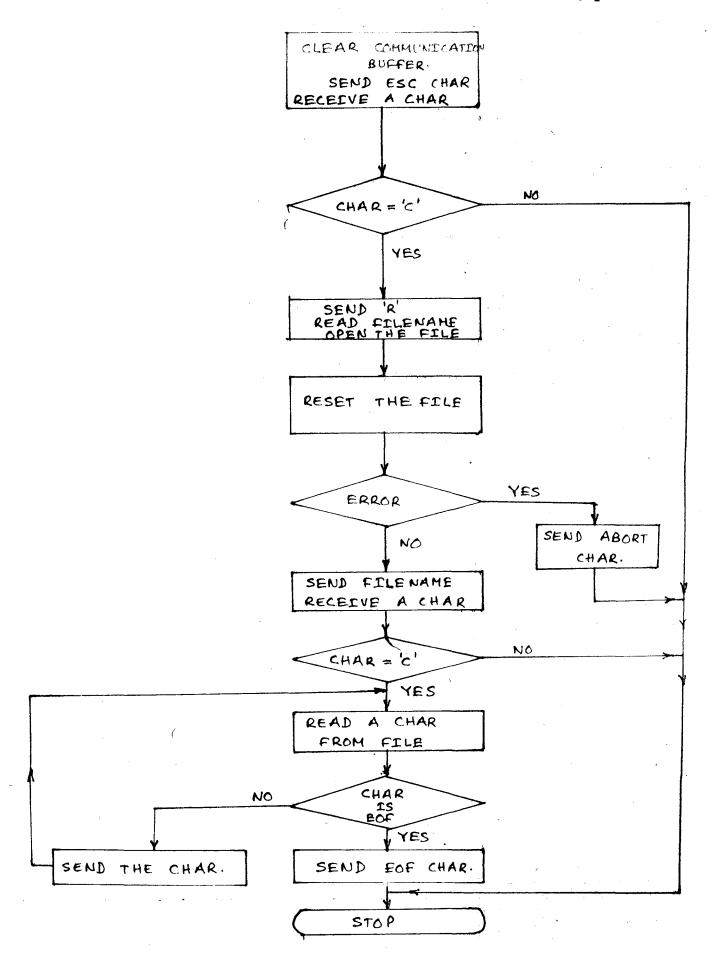

This SENDFILE procedure reads the filename and opens that file. If the file is not existing, it sends an error message to the other pc, then disables multitasking and returns to the main program. It reads the file block wise and sends the characters one after the other. Then it closes the file and disables multitasking. The flow chart is given in fig 3.8

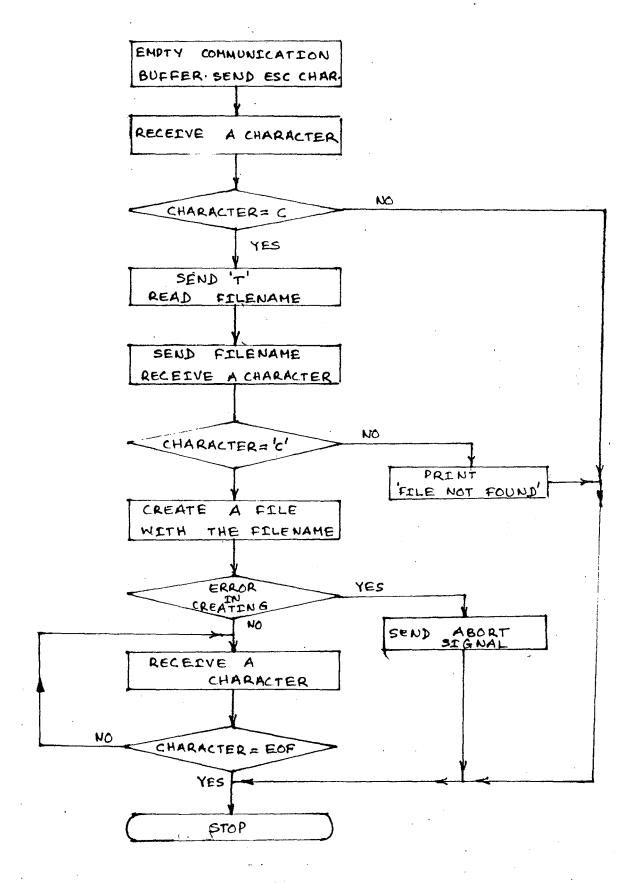

GETFILE: This procedure is called when a user on pc2 mails a file. It disables the multitasking by calling NOSWAP, reads the filename sent by pc2, creats a file with that name and reads the contents of the file sent by pc2 and stores them in disk till the end of file is encountered. If it is unable to create a file, it sends an error message to the other pc.

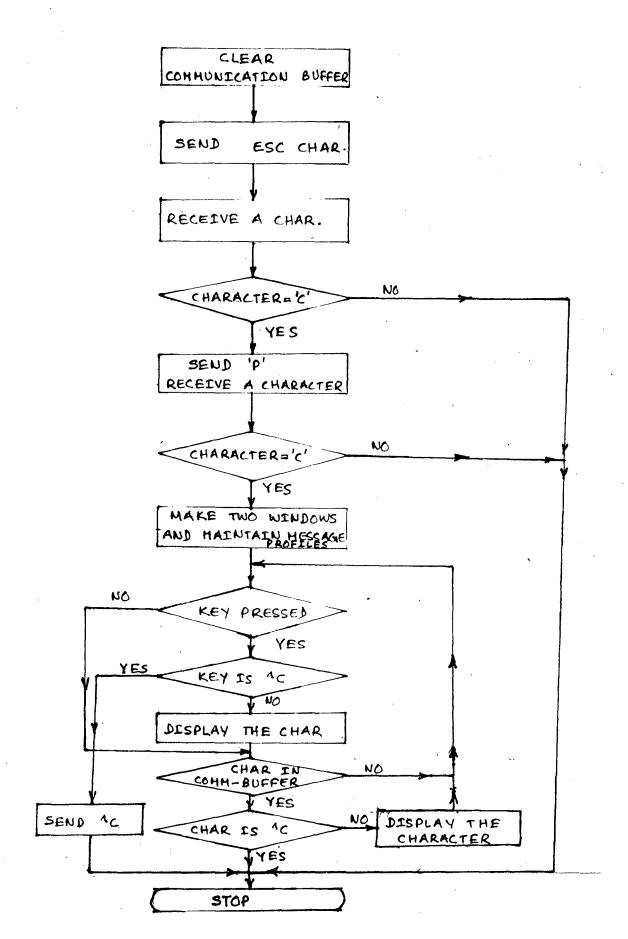

SPEAK: This procedure is called, when a user on pc2 makes a phone call to pc1. It prompts the user for his permission. If the permission is granted, it creats two windows on the screen and maintains the message profiles in these two windows. It displays both the data sent and data received. This phone utility is terminated with a c, and the other user is also taken out of PHONE.

FIG 3.9

COMMAND: This procedure is called after the execution of the DOS call, specified by the user on pc2. This will send the output of that command to the pc2, which is stored in the file C:REDIRE CT.

The main program FACILITY is called from the assembly progarm PCNET by keeping the request in the common variable TRAY. It checks the value in TRAY. If it is -

- 'T' calls SENDFILE procedure.

- 'R' calls GETFILE procedure.

- 'P' calls SPEAK procedure.

- 'D' calls COMMAND procedure.

After the execution of the procedure, it returns control to the PCNET which returns control to the user. The flow chart is given in fig 3.9.

- 3.3.6 PHONE: This is an independent pascal program and has to be run separately to invoke PHONE facility. To use the phone facility, PHONE has be run on one of the pcs. When run, it checks to see if the other user is interested in PHONE and proceeds just SPEAK procedure described above. The flowchart is given in Fig 3.10.

- 3.3.7 MAIL: This is an independent program written in pascal. It is invoked when a user wants to mail a file to the other user. It sends the filename and the contents of the file to the other user. Before sending a character, a check is made to see if an XOFF character is sent by the other pc. If an XOFF is received, character transmission is suspended till an XON character is received. This makes sure that characters

are not lost due to buffer overflow. If there is any error in creating a file at the other node, it will receive an error indicator and aborts with an appropriate message. The flowchart is given in Fig 3.11.

3.3.8 ASKFILE: This an independent pascal program, which has to be run to request a file transfer from the other node. The other system sends the data in the file with the consent of the user. It sends the data in the file (if the file is existing). ASKFILE receives this data and stores it in a file. If the file is not existing at the other node, it receives an error message and aborts with an appropriate message. The flowchart is given in Fig 3.12.

3.3.9 DOS : When a user on pcl wants to run a program pc2, he has to invoke this program. Typical application of this facility is to use the printer connected to the other pc with a simple command from this pc.Similarly he can see the directory on the other pc from his pc. This program when run, prompts for the command to be run on the other pc. This command is sent to the other pc for execution. Any output of this command is redirected back to the host pc displayedon screen. When the command is entered, this command is appended with C:REDIRE#CT string ,and a new string is created with the string length at the first position followed by C. This string is then sent to the other pc,where it is executed by loading the COMMAND.COM. outout is buffered in to a file and is transmitted back to

FIG 3-12

this PC and is dsplayed on the screen.

#### IV INSTRUCTIONS FOR USE

To use the PC to PC communication utilities, proceed as follows - step1 : install C drive and copy COMMAND.COM onto it.

step2 : run RESPC

step3 : run FACILITY

step4 : run PCNET

You need to follow the above steps on both the PCs only once, when you boot the system.

If you are currently using PC1 and want to get a file from PC2 ,  $\mbox{run}$  ASKFILE .

When prompted, give the filename. With the approval of the other user, the file will be transferred to your disk.

To mail a file to the other user ,run MAIL. When prompted, give the filename. With the consent of the other user, the file will be mailed to him.

To make a phone with the other user, run PHONE . The other user will be informed and if interested, will go into PHONE and you can proceed. Exit the phone with ^C.

To run DOS commands on the other pc, run the program DOS. When prompted, give the command you want to execute. You can use this facility to print your file on the printer connected to the other pc. However, to print a file, first you have to mail the file to the other system. You can also see the directory of the other user.

# V FUTURE EXTENSIONS AND MODIFICATIONS

This package can be extended and modified to qive various other facilities to the user.

The file transfer utilities can be modified to include sub directory and/or wild card specifications. These file transfer utilities transfer only character files. Integer files like object files can not be transferred. The program can be modified to transfer integer files by using character stuffing.

This PC to PC communication facility can be extended to connect more than two pcs. Collision detection should be incorporated. If at least one of the system is a PC-XT, it can serve as a file server and a typical LAN sytem can be build up. The ultimate and most usefull architecture is the one, in which any PC can either communicate with the other PC or with VAX with simple software control.

#

| ADD                   | ADD destination, source Addition |         |       |                | Flago X XXXXX      |  |

|-----------------------|----------------------------------|---------|-------|----------------|--------------------|--|

| Operands              | Operands Clocks Transfers' Bytes |         | Byles | Coding Example |                    |  |

| register, register    | ·                                | 3       | -     | 2              | ADD CX DX          |  |

| register, memory      | Ä                                | 9 . EA  | 1     | 2.4            | ADD DI. [BX] ALPHA |  |

| memory, register      | -                                | 16 . EA | 2     | 2.4            | ADD TEMP CL        |  |

| register, immediate   |                                  | 4       | !     | 3.4            | ADD CL 2           |  |

| memory, immediate     |                                  | 17 . EA | 2     | 3.6            | ADD ALPHA, 2       |  |

| accumulator immediate |                                  | 4       | -     | 2.3            | ADD AX. 200        |  |

|                       |                                  | ŧ l     |       | Į              | l.                 |  |

| AND                    | AND destination, source<br>Logical and |         |            |       | Flags O DITSZAPC  |  |

|------------------------|----------------------------------------|---------|------------|-------|-------------------|--|

| Operanda               |                                        | Clocks  | Transfera* | Byles | Costng Example    |  |

| register, register     |                                        | 3       | -          | 3     | AND AL.BL         |  |

| register, memory       |                                        | DOEA    | 1          | 2.4   | AND CX.FLAG_WORD  |  |

| memory, register       |                                        | 18 + EA | 2          | 2.4   | AND ASCHIDILAL    |  |

| register, immediate    |                                        | 4       |            | 3-4   | AND CX.0FOH       |  |

| memory, immediate      |                                        | 17 + EA | 2          | 3-8   | AND BETA, OTH     |  |

| accumulator, immediate |                                        |         | _          | 2-3   | AND AX. 010100000 |  |

| CALL                                     | CALL target Call a procedure |            |       |                                 |  |

|------------------------------------------|------------------------------|------------|-------|---------------------------------|--|

| Operar                                   | de Clechs                    | Transfers* | Byles | Cading Examples  CALL NEAR_PROC |  |

| near-proc                                | 19                           | 1          | 3     |                                 |  |

| far-proc                                 | 28                           | 2          | 5     | CALL FAR PROC                   |  |

| memptr 16                                | 21 + EA                      | 2          | 2-4   | CALL PROC_TABLE ISI             |  |

| 16 11 11 11 11 11 11 11 11 11 11 11 11 1 | 16                           | 1          | 2     | CALL AX                         |  |

| memptr 32                                | 37 + EA                      | 4 .        | 2-4   | CALL BX TASK SI                 |  |

|                                          | g g                          | 1 .        | I     |                                 |  |

| СВЖ           |  | CBW (no operands)<br>Convert byte to word |            |       | Plaga ODITSZAPC |

|---------------|--|-------------------------------------------|------------|-------|-----------------|

| Operanda      |  | Clocks                                    | Transfers* | Bytes | Coding Exemple  |

| (no operands) |  | 2                                         | -          | 1     | CBW             |

| CLC -         | CLC (no<br>Cleer ca | operands)<br>rry Hag |            | Flego ODITSZAP | CO             |  |

|---------------|---------------------|----------------------|------------|----------------|----------------|--|

| Operands      |                     | Cleaks               | Transfers* | Syles          | Coding Example |  |

| (no operands) |                     | 5                    |            | 1              | crc            |  |

|               |  | (sbratego<br>gall notice | ,          | Flaga ODITSZAPC |                |

|---------------|--|--------------------------|------------|-----------------|----------------|

| Operande      |  | Clecks                   | Translars* | Bytes           | Coding Example |

| (no operanda) |  | 2                        | _          | 1               | CLO.           |

<sup>\*</sup> For the 8085, add four clocks for each 16-bit word transfer with an odd address. For the 8088, add four clocks for each 16-bit word transfer. Pinemonics © Intel, 1978.

| CLI           |   | operandsi<br>errupt llag |            | Flags ODITSZAPC |                |

|---------------|---|--------------------------|------------|-----------------|----------------|

| Operands      |   | Clocks                   | Transfers* | Byles           | Coding Example |

| (no operands) | · | 2                        |            | ,               | CLI            |

| CMC           | CMC ind o |        |            | Flags ODITSZAP.C |                |

|---------------|-----------|--------|------------|------------------|----------------|

| Operands      |           | Clocks | Translers* | Bytes            | Coding Example |

| (no operands) |           | ?      | <u></u>    | 1                | CMC            |

| 11.1011                         |  | stination sc<br>edestinatio | ource<br>in to source |       | Flags O DITSZAPC      |

|---------------------------------|--|-----------------------------|-----------------------|-------|-----------------------|

|                                 |  | Clocks                      | Transfers*            | Byles | Coding Example        |

| register register               |  | 3                           |                       | 2     | CMP Bx Cx             |

| register memory                 |  | 9 . EA                      |                       | 2.4   | CMP DH ALPHA          |

| memor, register                 |  | 9 . EA                      | ١ .                   | 2.4   | CMP BP+2: SI          |

| respective in specificates      |  | 4                           | -                     | 3.4   | CMP BL-02H            |

| ettantragie , ort ettantfalaler |  | 10 - EA                     | 1                     | 3.6   | CMP BY RADAR DI 3420H |

| acquite afor mererbate          |  | <b>3</b>                    | -                     | 2.3   | CMP AL .0001000018    |

| CMPS                                                       | 1 -    | destisting si    | ource-string | Flags ODITSZAPC |                                  |  |  |

|------------------------------------------------------------|--------|------------------|--------------|-----------------|----------------------------------|--|--|

| Operands                                                   |        | Clocks           | Transfers*   | Byles           | Coding Example                   |  |  |

| dest string source string<br>(repeat) dest string source s | itring | 22<br>9 + 22 rep | 2<br>2 rep   | 1               | CMPS BUFFE BUFFE REPECMPS ID KEY |  |  |

| CWD           | 1 | operands<br>ob of brow |            | Flags |                |

|---------------|---|------------------------|------------|-------|----------------|

| Operands      |   | Clocks                 | Transfers* | Byles | Coding Example |

| (no operands) |   | . 5                    | -          | 1     | CWD .          |

| DAA           | 1 | operands)<br>adjust for a |            | Flags ODITSZAPC |                |

|---------------|---|---------------------------|------------|-----------------|----------------|

| Operands      |   | Clocks                    | Transfers* | Bylos           | Coding Example |

| (no operands) |   | 8                         | _          | \ 1             | DAA            |

| DAS           | 1 - | operandsi<br>adjust for s | subtraction |       | Flags | 0 D I | T S<br>X | ZA   | PC |

|---------------|-----|---------------------------|-------------|-------|-------|-------|----------|------|----|

| Operands      |     | Clocks                    | Transfors*  | Byles | С     | oding | zamp     | ) le |    |

| (no operands) |     | / 4                       |             | 1     | DAS   | _     |          |      |    |

<sup>\*</sup> For the 8086, add four clocks for each 16-bit word transfer with an odd address. For the 8088, add-four clocks for each 16-bit word transfer. Mnemonics © Intel, 1978

| DEC      | DEC itestination<br>Decrement by 1 |            |       | Flags ODITSZAPC |

|----------|------------------------------------|------------|-------|-----------------|

| Operands | Clocks                             | Transfers* | Byles | Coding Example  |

| recib    | 7                                  | -          | 1     | DEC AX .        |

| regs     | j                                  | _          | 2     | DEC AL          |

| memory   | 1.19 · EA                          | 2          | 2.4   | DEC ARRAY (SI)  |

| DIV      | DIV source<br>Division, unsigned |            |       | Flago U UUUUU  |

|----------|----------------------------------|------------|-------|----------------|

| Operands | Clecus                           | Transfers* | Bytes | Coding Example |

| regs     | 80-90                            |            | 2     | DIV CL         |

| reg16    | 166-162                          |            | 2     | DIV BX         |

| mem8     | 186.93)<br>• EA                  | ,          | 2.4   | DIV ALPHA      |

| mem16    | (150-168)<br>+ £ A               | 1          | 2:4   | DIV TABLE [SI] |

| ESC                | ESC enternal opcode source<br>Escape |        | de source  | ,     | Flags ODITSZAP C  |  |  |

|--------------------|--------------------------------------|--------|------------|-------|-------------------|--|--|

| Operands           |                                      | Clecks | Transfers* | Bytes | Coding Example    |  |  |

| immediate memory   |                                      | 8 . EA | 1          | 2.4   | ESC B. ARRAY [SI] |  |  |

| immediate register |                                      | 7      | -          | 2     | ESC 20.AL         |  |  |

|                    |                                      | 1 .    | Į          | 1     |                   |  |  |

| HLT           | HLT (no e | operands) |            |       | Flaga ODITSZAPC |

|---------------|-----------|-----------|------------|-------|-----------------|

| Operanda      |           | Clocks    | Transfors* | Byles | Coding Example  |

| (no operands) |           | 2         | -          | 1 :   | HLT             |

| IDIV   | IDIV source<br>Integer division | 20:           | 1     | Flaga U UUUUU        |

|--------|---------------------------------|---------------|-------|----------------------|

| Opera  | nds Ck                          | cho Transforo | Bytes | Coding Example       |

| 800    | 101                             | -112 -        | 2     | IDIV BL              |

| 10g16  | 169                             | -184 -        | 2     | IDIV.CX              |

| mem8   | 1107                            | -118) 1       | 2.4   | IDIV DIVISOR_BYTE SI |

|        | <b>.</b> .                      | EA            | 1     |                      |

| mein16 | t ·                             | -190) 1       | 2-4   | IDIV BX DIVISOR_WORD |

| 1      |                                 | EA            | 1     | '                    |

| IMUL     |  | IMUL source<br>Integer multiplication |            | Flags X UUUUX |                         |

|----------|--|---------------------------------------|------------|---------------|-------------------------|

| Operands |  | Clochs                                | Transfers* | Bylos         | Coding Example          |

| reg8     |  | 80-98                                 | :          | 2             | IMUL CL                 |

| reg16    |  | 128-154                               | Ξ          | 2             | IMUL BX                 |

| mém8     |  | (85-104)<br>+ EA                      | 1          | 2-4           | IMUL RATE BYTE          |

| mem16    |  | (134-160)                             | 1          | 2.4           | IMUL RATE WORD BP [ DI) |

| IN                                  | l l   | mulator.por<br>te or word | î          |       | Flaga ODITSZAPC            |

|-------------------------------------|-------|---------------------------|------------|-------|----------------------------|

| Operar                              | rds . | Clocks                    | Pronsters* | Bytos | Coding Example             |

| accumulator, immod8 accumulator. DX |       | 10                        | 1          | 2     | IN AL. OFFEAH<br>IN AX. DX |

|                                     |       |                           |            |       |                            |

| INC    | INC desi |         |            |       | Fia 18 X X X X  |

|--------|----------|---------|------------|-------|-----------------|

| Opera  | ebn      | Clocks  | Proneters* | Byles | Coding Example  |

| 80e1   |          | 2       | -          | 1,    | INC BL          |

| memory |          | 19 - EA | 2          | 2.4   | INC ALPHA DI BX |

| INT                                    | INT interr<br>Interrupt | upi-lypo |            | 1 ( ) | Flags ODITSZAPC  |

|----------------------------------------|-------------------------|----------|------------|-------|------------------|

| Operanda                               |                         | Clecks   | Transfers* | 89100 | · Coding Example |

| immed8 (type = 3)<br>immed8 (type = 3) |                         | 52<br>51 | 5<br>5     | 1 2   | INT 3.:          |

| INTR      |          | ernal mas<br>in RTMI hi | kable interrup<br>d IF=1 | 0     | Flogs GO       |

|-----------|----------|-------------------------|--------------------------|-------|----------------|

|           | Operands | Clocks                  | Pranalora*               | Byles | Coding Example |

| (no opera | nds)     | 61                      | 7                        | N/A   | NIA            |

| INTO          | INTO (no op<br>interrupt if o |        |            | ٠.    | Flegs ODITSZAP |

|---------------|-------------------------------|--------|------------|-------|----------------|

| Operando      | C                             | locks  | Transfers* | Bylos | Coding Example |

| (no operands) | 5                             | 3 or 6 | 5          | 1     | INTO           |

| IRET                      | IRET (no o                                         |                                                 |                      |            | Flaga PRARRRR                                                           |

|---------------------------|----------------------------------------------------|-------------------------------------------------|----------------------|------------|-------------------------------------------------------------------------|

| Operands                  |                                                    | Clocks                                          | Transfers*           | Byles      | Coding Example                                                          |

| (no operands)             |                                                    | . 24                                            | 3                    | 1          | IRÉT                                                                    |

| JA/JNBE                   | JA/JNBE<br>Jump il su                              |                                                 | ol<br>p if not below | nor equa   | Flags ODITSZAP                                                          |

| Operands                  |                                                    | Clocks                                          | Transfers*           | Bytes      | Coding Example                                                          |

| short-label               | Ì                                                  | 16 01 4                                         |                      | 2          | JA ABOVE                                                                |

| JAE/JNB                   | BML/3AL<br>da li qmut                              |                                                 | el<br>ual/Jump il no | ot below   | Flags ODITSZAP (                                                        |

| Operands                  |                                                    | Clocks                                          | Transfers*           | Bytes      | Coding Example                                                          |

| short-labet               |                                                    | 16 or 4                                         | -                    | 2          | JAE ABOVE EQUAL                                                         |

| JB/JNAE                   |                                                    | E short-label below/Jump if not above nor equal |                      |            | Flags ODITSZAP (                                                        |

| Operands /                |                                                    | Clocks                                          | Transfers*           | Byles      | Coding Example                                                          |

| short-label               |                                                    | 16 or 4                                         |                      | 2          | JB BELOW                                                                |

| J8E/JNA                   | JBE/JHA<br>Jump il be                              |                                                 | al<br>ual/Jump if no | ol above   | Flogs ODITSZAPO                                                         |

| Operanda                  |                                                    | Clocks                                          | Transfers*           | Bytes      | Coding Example                                                          |

| short-label               |                                                    | 16 or 4                                         | \ <del>-</del>       | 2          | JVOBA TOH ANL                                                           |

| JC                        | JC short-li<br>Jump it ca                          |                                                 |                      |            | Flogs ODITSZAP (                                                        |

| 0                         |                                                    | Clasha                                          | Transfers*           | Byles      | Coding Example                                                          |

| Operands                  |                                                    | Clocks                                          | I I BUBIETS          | 1 0,.00    | oodung casmpia                                                          |

| short-label               |                                                    | 16 or 4                                         |                      | 2          | JC CARRY SET                                                            |