# INTERFACING INCREMENTAL PLOTTER WITH EC 1020 B COMPUTER SYSTEM

Dissertation submitted in partial fulfilment of the requirements for the degree of MASTER OF PHILOSOPHY

SATYA NARAYAN SINGH

124p.+fig.

School of Computer and Systems Sciences

JAWAHARLAL NEHRU UNIVERSITY

NEW DELHI-110067

#### CERTIFICATE

This is to certify that the dissertation " INTERPACING INCREMENTAL PLOTTER WITH EC 1020B COLPUTER SYSTEM " submitted for the partial fulfilment of the requirements for the degree of Haster of Philosophy, by Setyanarayan Singh, is a record of bonafide work. The research work embodied in this dessertation has been carried on in School of Computer and Systems Sciences, Javaharlal Nebru University, New Delhi-110067. The work is original and has never been submitted in part or in full for any degree or diploma of any University.

B.S. Willie

SCHOOL OF COMPUTER AND SYSTEMS SCIENCES JATAHARLAL NEVRU UNIVERSITY

HET DELEI

1981

#### ACHIOVLEDGE TELT

It is my pleasure to acknowledge the wide variety of assistance the staff members, colleagues, friends, and others have provided me in finishing the work of this dissertation.

I am particularly indebted to my -supervisors, Prof. (1.P. Dukherjee and Dr. D.6. Khurana for the valuable help they have given me althrough the development of this work. Tords can hardly describe the gratitude I ove to Dr.P. Bismas and Dr. A.K. Majumdar for their constant guidance and encouragements given to me throughout the research work. Special thanks are also due to Mr. D.K. Roy for being always helpful in the laboratory work.

other friends deserve my sincere thanks for sparing their valuable time for sketching the diagrams given in this dissertation and the proof reading work. I am also grateful to my parents and family members for their love and affection, which helped me a lot in my studies.

Last but not the least, I wish to sincerely thank

my wife for her unfailing support, patience and co-operation

without which it would have been extremely difficult for

me to complete this work.

I also wish to acknowledge gratefully the financial assistance  $U_*G_*C_*$  had given me during my tenure as student in  $J_*U_*U_*$

New Delhi 5.1.82 BATYADARAYAN SIDGH

# TADLE OF COUTENTS

| ACREOTLENGEL | ente |                                                 | PAGE |

|--------------|------|-------------------------------------------------|------|

| SYPOPEIG     |      |                                                 |      |

| CHAPTER = 1  | INT  | ODUCTION                                        | 1    |

| Chapter - 2  | CEDE | RAL INTERPACIFE CONSIDERATION                   | 3    |

|              | 5-1  | Preliminaries                                   | 3    |

|              | 2-2  | Interface Functions                             | 4    |

|              | 2-3  | Concept of the Standard<br>Interface Codule     | 6    |

|              | 8=4  | Pactor Affecting On Interface<br>Design         | 7    |

|              |      | 2-4.1 Data Transfer Techniques                  | 7    |

|              |      | 2-4.8 I/O Structure of the Computer             | 9    |

|              |      | 2-4.3 I/O Device Characteristics                | 10   |

|              | 2-5  | Specification of a Computer<br>Interface        | 11   |

|              | 2-6  | Incremental Flotter Interfacing with a Computer | 12   |

| CHAPTER - 3  |      | CHARREL OF EC 1020/30B COMPUTER +               |      |

|              | 3-1  | Organisation of EC=1020/D Computer              | 18   |

|              | 3-8  | Input/Output System                             | 17   |

|              |      | 3-2.1 1/0 Interface                             | 18   |

|              |      | 3-2.2 Channels                                  | 18   |

|              |      | 3-2.3 I/O Instructions                          | 31   |

|              |      | 3-2.4 1/0 Operation Initiation                  | 83   |

|              |      | 3-2.5 I/O Command                               | 25   |

|            |     | 3-2-6             | I/O Terminator                                     | <del>59</del> |

|------------|-----|-------------------|----------------------------------------------------|---------------|

|            |     | 3-2.7             | I/O Interruption                                   | 30            |

|            |     | 3+2+8             | Basic Procedure For a Data<br>Transfer Operation   | 31            |

|            | 3-3 | <b>Eultipl</b>    | lexor Channel                                      | 32            |

|            |     | 3-3,1             | Basic Data Path<br>And Block Diagrams              | 32            |

|            |     | 3-3.2             | Microprogram Control of the I/O System             | 33            |

|            |     | 3-3.3             | Eultiplexor Channel Block<br>Diagram And Data Flow | 33            |

|            |     | 3-3.4             | Hardware of the MUX<br>Channels                    | 38            |

|            | 3-4 | General<br>Eultip | l 1/0 Interface Sequence<br>Lexor Chahnel.         | 39            |

| CHAPTER -4 |     |                   |                                                    |               |

|            |     | System            | Component Description                              | 45            |

|            | 4-1 | System            | Block Diagram                                      | 45            |

|            | 4-2 |                   | terface Structure<br>gnal Sequences.               | 47            |

|            |     | 4-2,1             | Line Defination                                    | 50            |

|            |     | 4-2.2             | System CC-1020B<br>Interlocking Bules              | 56            |

|            |     | 4-2.3             | Friority Assignment by Set-Out Routing             | 57            |

|            |     | 4-2-4             | Important Signal<br>Sequences                      | 60            |

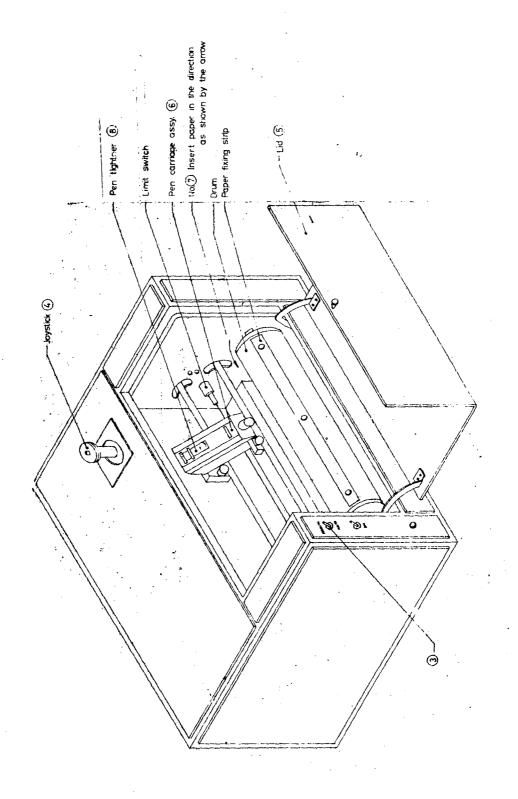

|            | 4-3 | GT-160            | Incremental Plotter                                | 69            |

|            |     | 4-3.1             | Punction                                           | 69            |

|            |     | 4-3.2             | Operating Principle                                | 70            |

|            |     | 4-3.3             | General Epecifications                             | 72            |

|            |                 |                                                         | PAGE |

|------------|-----------------|---------------------------------------------------------|------|

|            |                 | 4-3.4 Input Requirement                                 | 73   |

|            |                 | 4-3.5 Operational Check-out and Operating Procedure     | 74   |

|            | 4-4             | Buffered Plotter Controller                             | 76   |

|            | 4-5             | Interfacing Requirements                                | 78   |

|            |                 | 4-5.1 Interfacing Requirements-<br>Incremental Plotter  | 78   |

|            |                 | 4-5.2 Interfacing Requirements-<br>EC-1020B Eux Channel | 79   |

| CHAPTER -5 |                 |                                                         |      |

|            |                 | Interface Design Description                            | 81   |

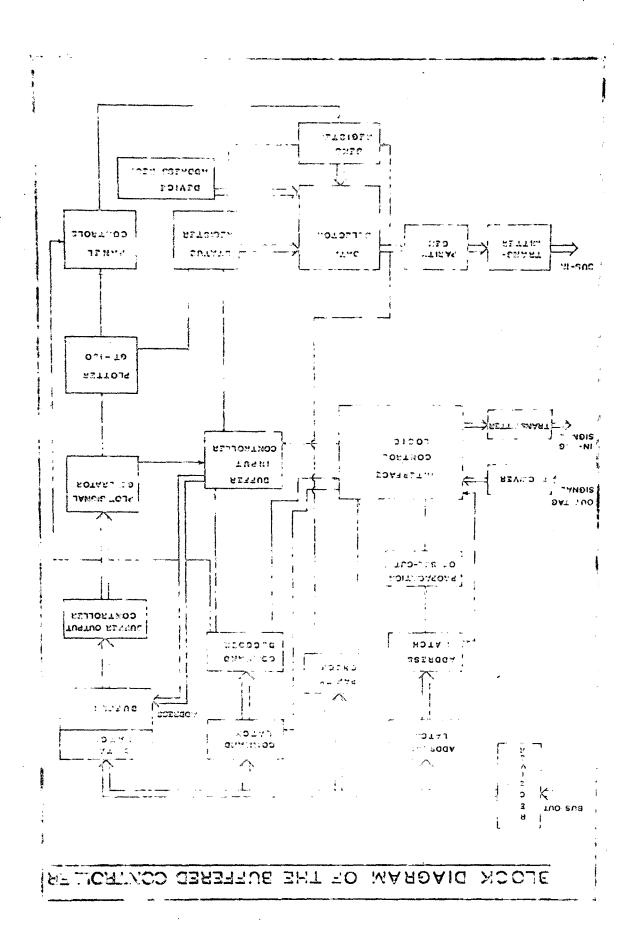

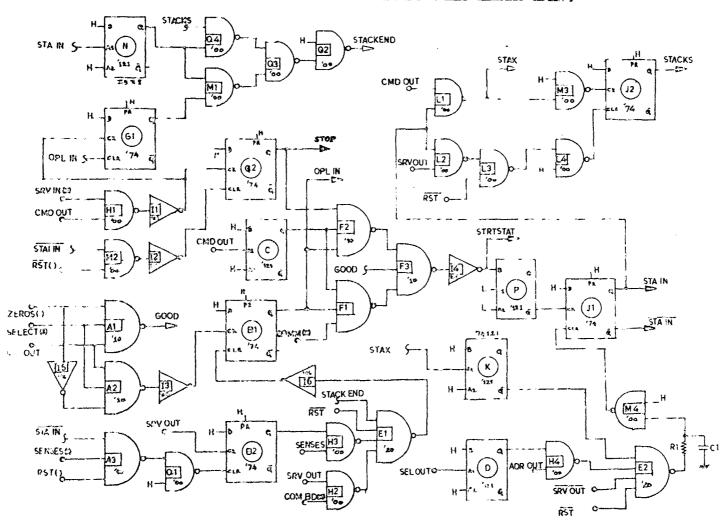

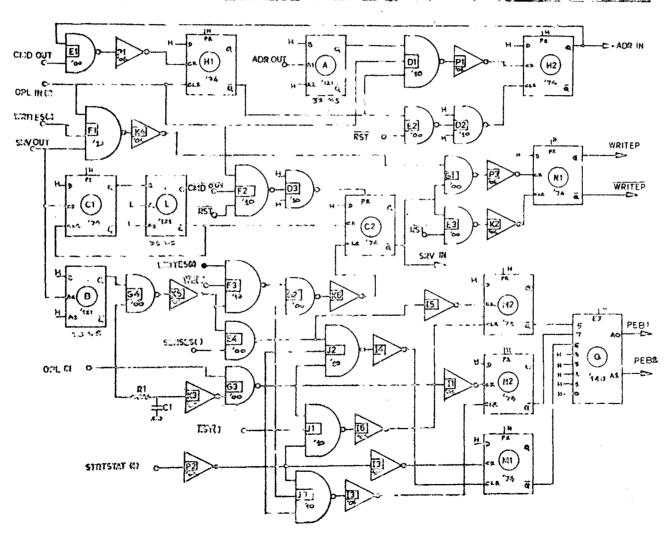

|            | 5-1             | Block Diagram of Buffered<br>Controller                 | 87   |

|            | 5-2             | Division of the Interface logic                         | 84   |

|            |                 | 5-2.1 Interface States                                  | 84   |

|            | ·               | 5-2.2 Buffer                                            | 86   |

|            |                 | 5-2.3 Command Structure                                 | 86   |

|            |                 | 5-2.4 Sense Byte & Status Bytes                         | 86   |

|            |                 | 5-2.5 IN-TAG Signals                                    | 87   |

|            |                 | 5-2.6 Device Address and Priority                       | 87   |

|            |                 | 5-2.7 Hain Block in Interface<br>Control                | 88   |

|            | 5-3             | Logic Diagram Notation                                  | 94   |

|            | 5 <del>-4</del> | Functional Description of PCB Cards                     | 96   |

|            |                 | 5-4.1 Bus-Out:Buffer Régister                           | 97   |

|            |                 | 5-4.2 Address Match                                     | 97   |

|            |                 | 5-4.3 Parity Check                                      | 98   |

|            |                 | 5-4.4 Accepting Command Code                            | 98   |

|           |     |         | ŗ                                       | AGE |

|-----------|-----|---------|-----------------------------------------|-----|

|           |     | 5-4.5   | Address, Commander ond Data States      | 99  |

|           |     | 5-4.6   | Operational-In And<br>Status-In Signal  | 88  |

|           |     | 5-4.7   | Duffer-Yrite-Pulse and                  | 101 |

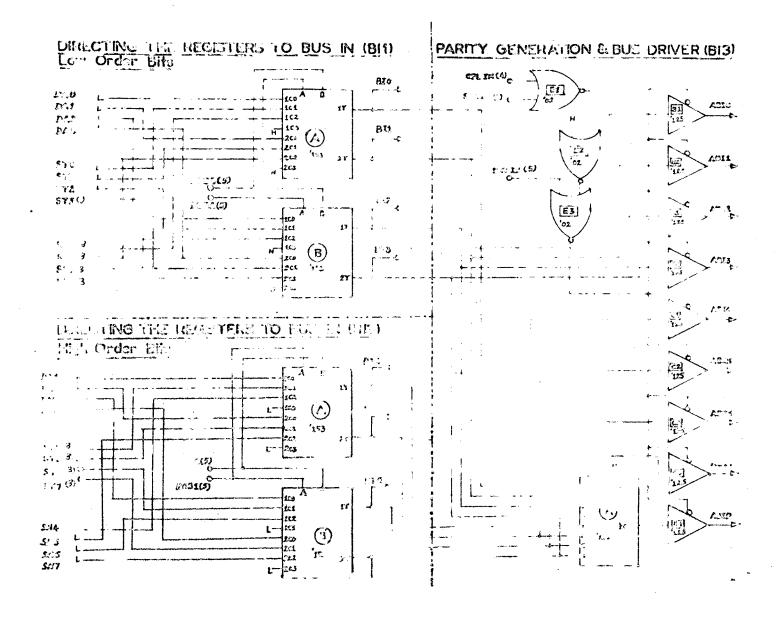

|           |     | 5-4-8   | Directing the register to Bus-In        | 104 |

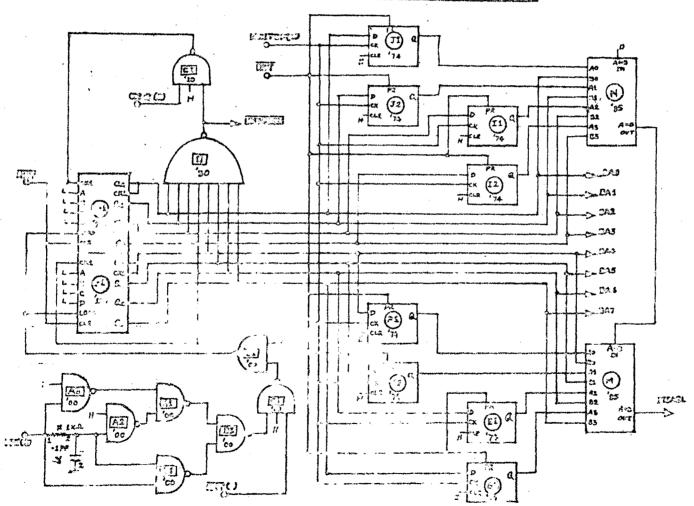

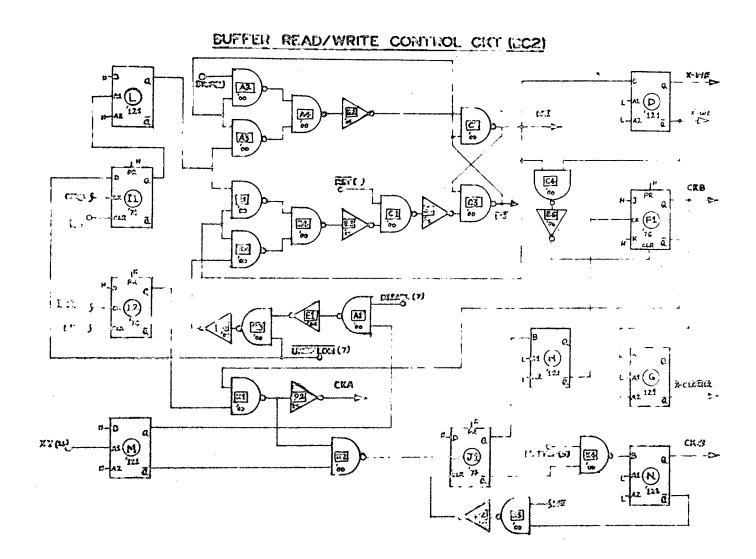

|           |     | 5-4.9   | Buffer Erite Control ckt.               | 104 |

|           |     | 5-4,10  | Buffer Resd/Write<br>Control Circuit    | 105 |

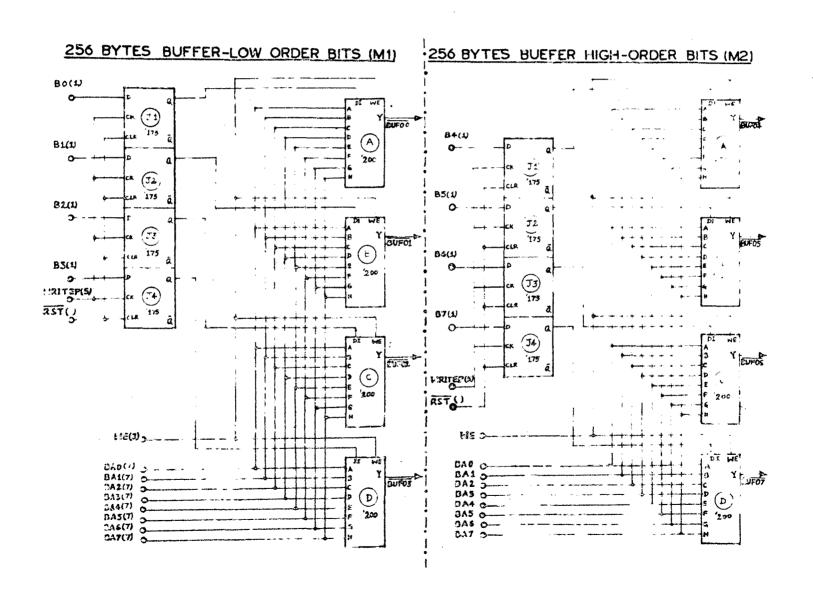

|           |     | 5-4.11  | 256 Bytes Buffer                        | 107 |

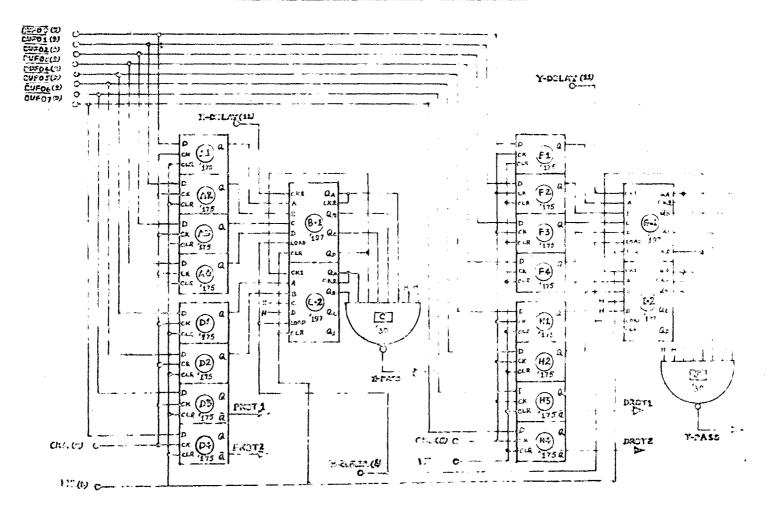

|           |     | 5-4,12  | Buffer Output Control ckt.              | 107 |

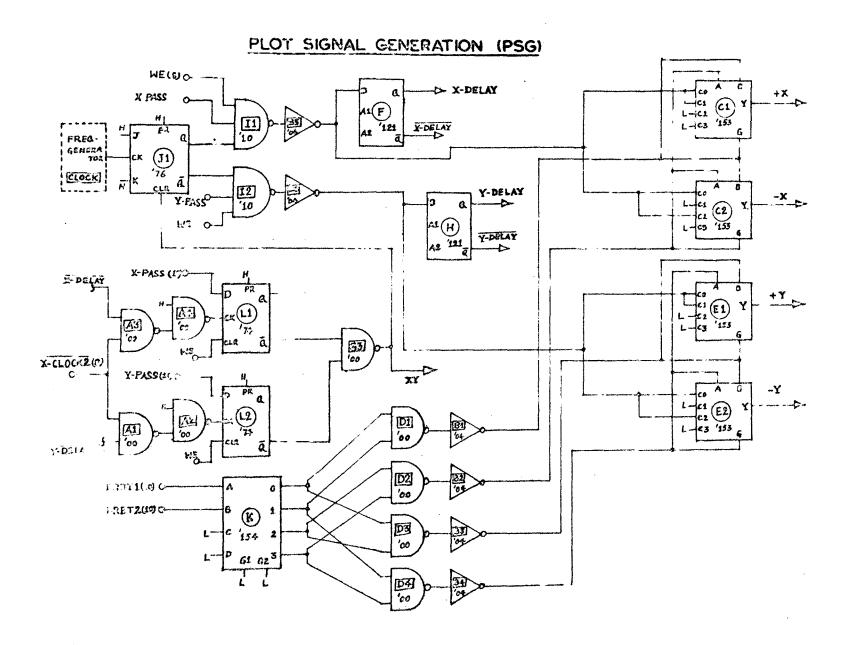

|           |     | 5-4.13  | Plot Signal Generation                  | 108 |

| CHAPTER - | 6   | Conclus | eion                                    |     |

|           | 5-1 | Genera] | Consideration                           | 109 |

|           | 6-2 | Future  | Extensions and Improvement              | 113 |

|           |     | 6-2,1   | Resolution of Plotting                  | 113 |

|           |     | 6-2.2   | lardware Technology                     | 114 |

|           |     | 6-2.3   | Plotter ckt. Improvement                | 114 |

|           |     | 6-2,4 ( | Card+Layout                             | 115 |

|           |     | 6-2.6   | Suffer Size                             | 118 |

|           |     |         | Interrupt Bendling<br>Pacility          | 116 |

|           | 6-3 | Coftra  | re Consideration                        | 116 |

|           |     | 6-3,1   | Traphics Software -<br>Jeneral Strategy | 116 |

|           |     | 8-3,2   | IOCS Software Specification             | 120 |

#### REFERENCES

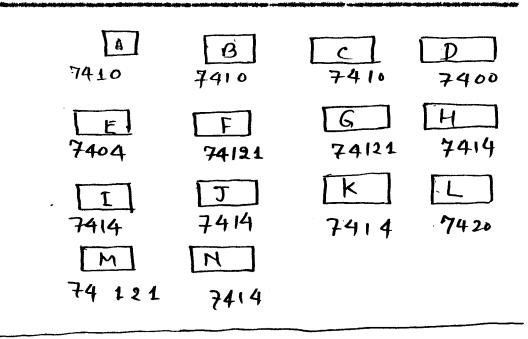

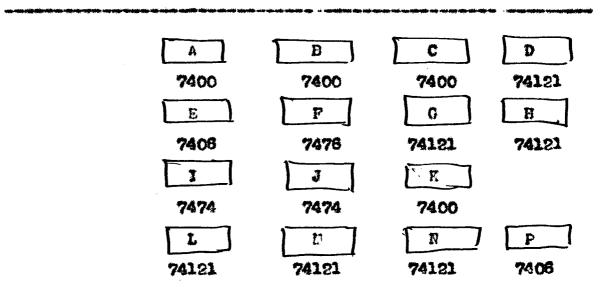

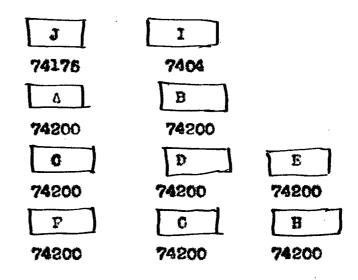

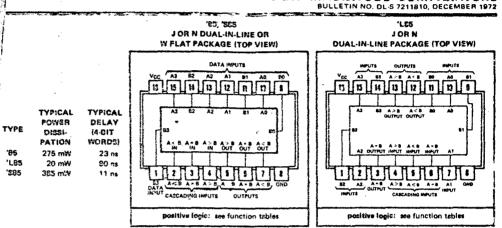

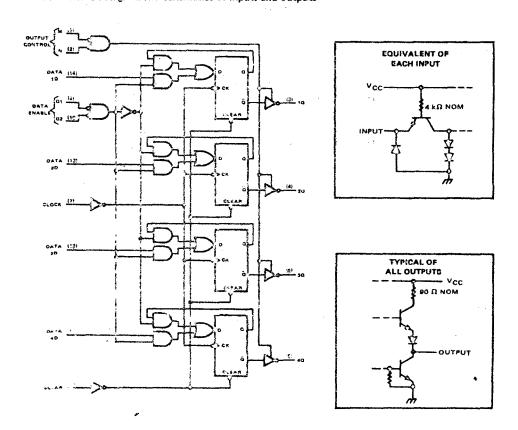

AFPENDIX - A Logic Diagram Implementation

APPENDIX - B PCB Cord-Layout

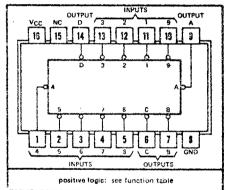

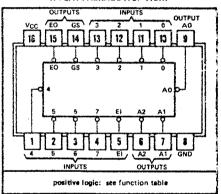

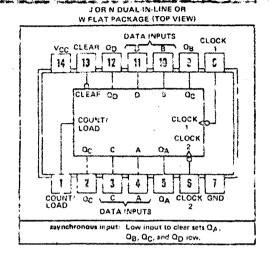

APPENDIX - C IC Chip Pin Assignment

### LIST OF PIGURES

# Figure Title

#### CHAPTER-3

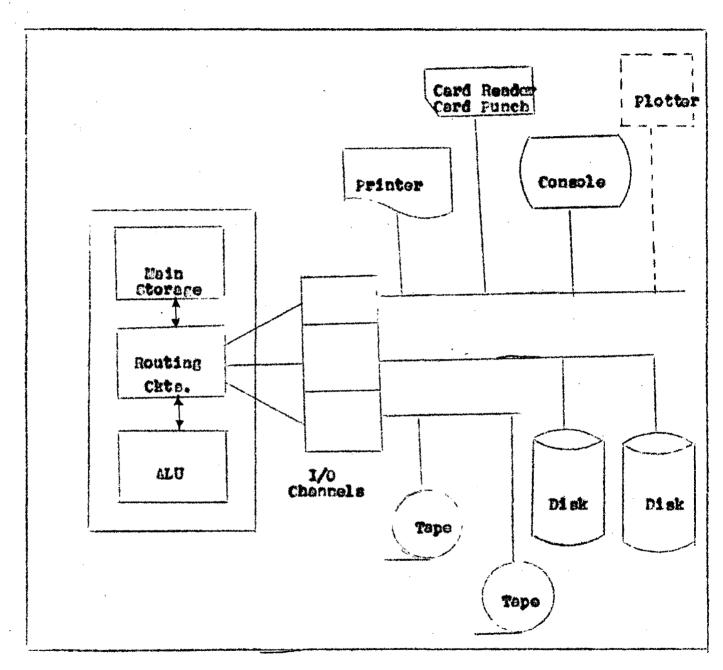

3.1 General Organisation of a Digital Computer

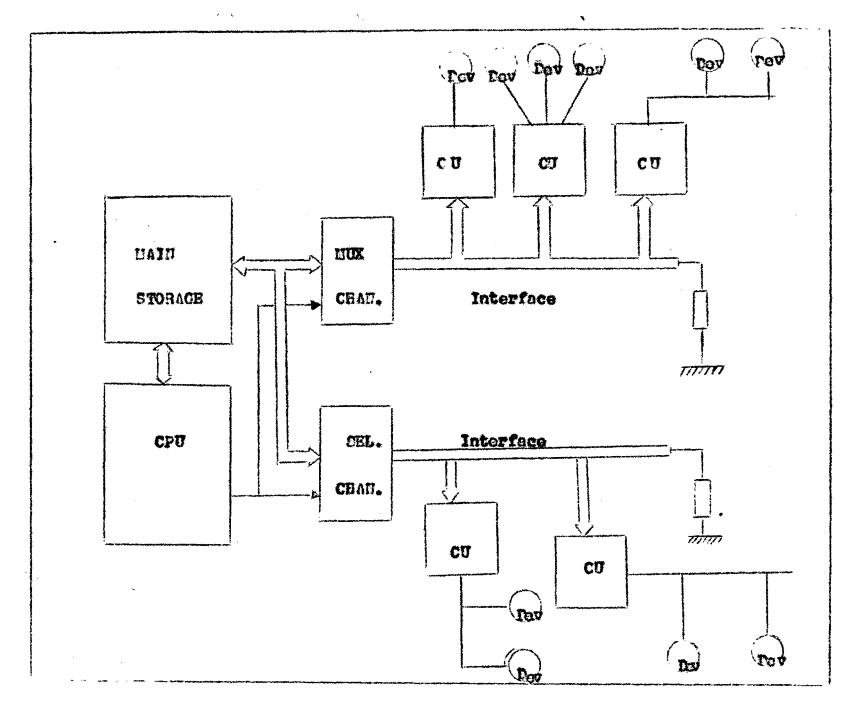

3.2 I/O Interface

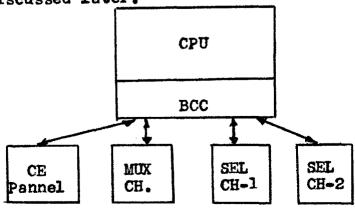

3.3 General Dlock Diagram of the CPU & 1/0 System

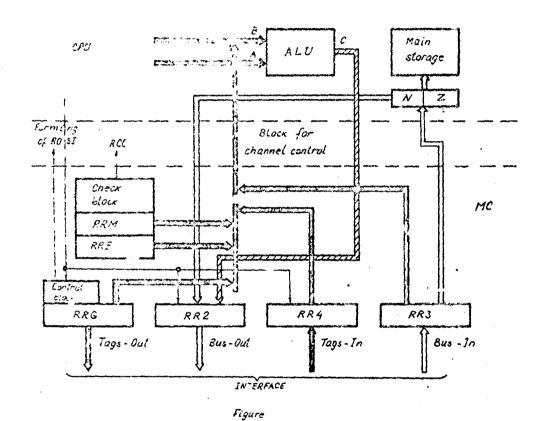

3.4 Block Diagram of MUX Channel

3.5 General I/O Sequence.

#### CHAPTER-4

4.1 Interconnection: Channel To Plotter

4.2 Line Definition

4.3 Priority Assignment By Select-Out Routing

4.4 Initial Selection

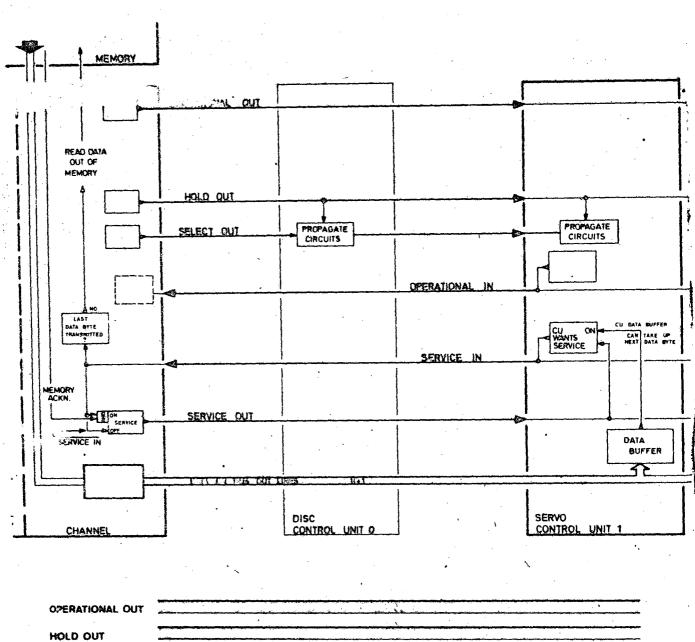

4.5 Erite (O/P) Data Transfer

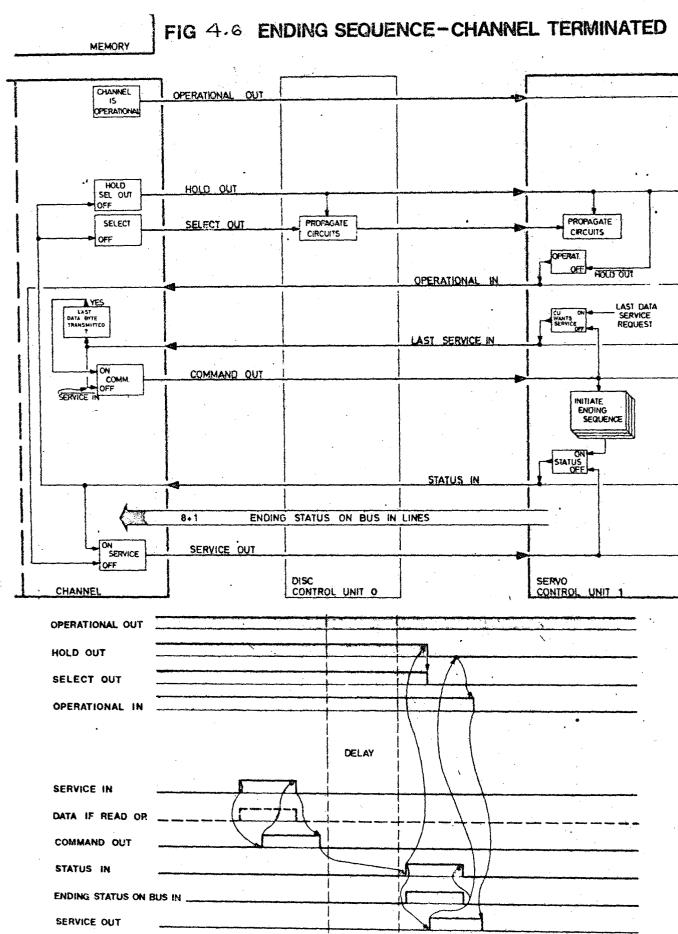

4.6 Ending Sequence-Channel Terminated

4.7 Plotter Assembly.

#### CHIEFER-6

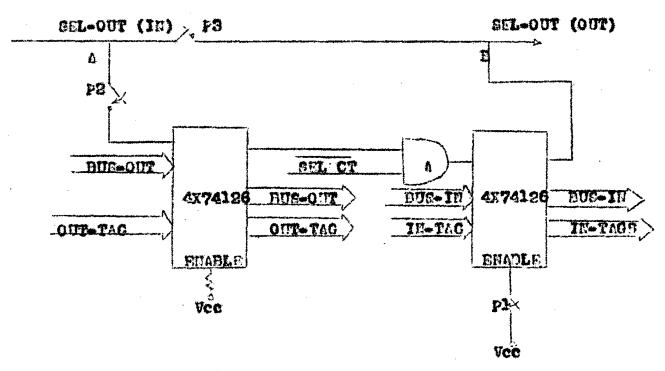

5.1 Selection Block

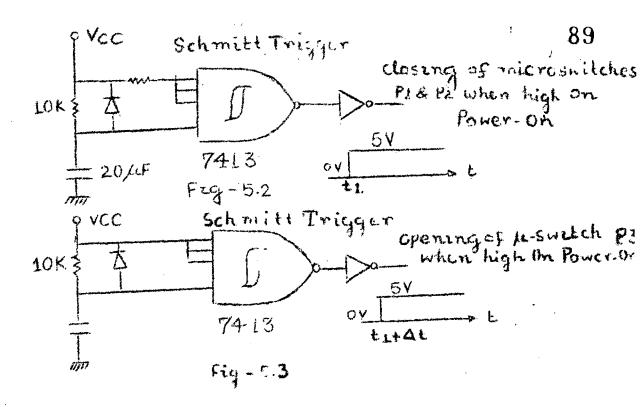

5.2 Schmitt Trigger for Closing Switches

5.3 Schmitt Trigger for Opening the Switch

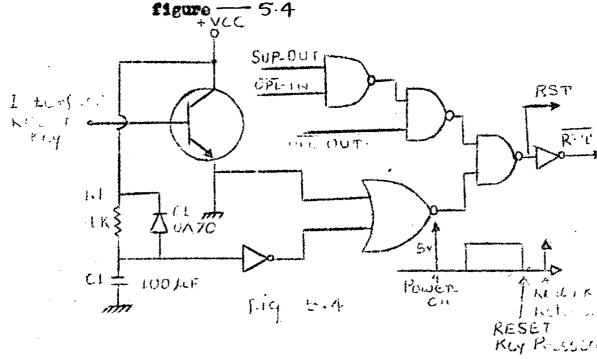

5.4 RESET CKT.

APPENDIX A Logic Diagrams of Implemented Interface ckts.

APPENDIX B PCB Card-Layouts

APPENDIX C Integrated ckt. Chips.

#### SYMOPSIS

popular, the need for the better presentation of its output has been constantly felt amongst the users. Since the conventional output device of the computer, i.e. Printer, can only present the data processing results in tabular form, the iinterpretation and analysis of result data remains a tedious work. The computer graphics is the solution of this problem. For the rapid translation of digital outputs into computer graphics for quick visual interpretation and analysis, the digital plotters are the best suited devices. The plotter can work on-line with the computer for computer graphics, if it is suitably interfaced with the host computers.

The incremental plotters are regarded as one of the slowest peripherals in a computer system. The objective of this project is to design the interface for an indigenous incremental plotter (KFLTROW) to be connected to the multiplexor channel of the EC 1020 system. The major objective of the design is to have a maximum possible throughput efficiency in the multiprogramming environment. This complete buffered interface supports multiplexor channel operation in the burst mode and allows the particular memory partition (stored output of the plot-program) to be released within a comparatively insignificant duration. As 'the EC 1020 interface follows the standard IBE 360/370 protocol,

so, with the minor modifications, the KELTRON GT-150 plotter can be connected on-line with any of the EC, IBM, or UNIVAC computer systems following similar protocol. In this thesis, most of the hardware circuitry has been designed and implemented in the laboratory and the detailed requirements of the IOCs software has been suggested.

## INTRODUCTION

Increasing demand on digital computer for use in large veriety of fields has necessitated the development of specialized interfaces so that they could be connected to different kind of external devices for processing jobs of different kind. Those external devices can be standard computer units such as disks, tape-driven, CRT displays, printers, and plotters; they can be various electrical, medical, or ther instruments that employ the computer for ON-LIME data processing; or they can be industrial equipments that employ the computer to supervise operations such as an automatic oil refinery or a computer-ized steel-rolling mill.

One can have the required interface for a particular application in any of the following three ways:

- i) It could be purchased entirely from the manufacturer;

- 11) It could be assembled using commercially available ckt. cords;

- iii) It could be designed from scratch and could then be built with individual integrated ckt. chips.

The third option has been followd in this work and the primary aim of this work has been to build up IC 1020/30B capability to support different applications in the field of Craphics. This has been done by interfacing

NFLTRON's GT 160- a dram type incremental plotter having six data input lines with EC 1020/30B system.

The project forms part of a laboratory development offert whose ultimate aim is to provide a graphics facility to the EC 1020/30B users in the areas of Research and development.

(

#### CHAPTER - 2

### GENERAL INTERPACIUS CONSIDERATIONS.

## 2-1 Preliminaries

Input/output dovices provide a means of communication between the computer and the outside world. A computer can have more than one I/O dovices connected to its I/O unit. Communication with any of I/O devices is established by selecting that device. I/O system of a computer should meet the following requirements.

- 1. Computer should not be tied down to the peripheral devices;

- 2. Computer should be independent of nature of I/O device i.e I/O system should be able to communicate with any of devices through proper interfaces;

- 3. It should account for difference in the type of information presented to or by I/O device, e.g the system might have to perform word " assembly before the data from a character oriented Input device could be transfered to the computer or word-disassembly for data word received from computer before sending to an output device;

- 4. The system should provide the way to write programs in such a way as to recover from unexpected conditions.

- 5. The system should have provisions to allow I/O devices to transfer data at their convenience regardless of memory availability at a particular moment e.g. buffer storage.

- 6. The addition or removal of any number of devices should not affect the computer from functioning normally.

The Interface should be built to take care of most of the above goals in herdware or leave some of them to be achieved by software so that the ratio of cost of herdware required to the improvement achieved is as small as possible.

## 2-2 Interface Functions

The following functions are performed by a typical interface between an I/O decice and computer;

- 1. To accept data from the computer or I/O device.

- 2. To transmit data to the computer or I/O device.

- 3. To execute the commands of the computer.

- 4. To transmit current status of operation .

- 5. To encode or decode data in terms of the required recording or reproducing methods.

- 6. To conitor overall device operation.

- 7. To account for difference in data transfer rates of the two seperate systems by providing buffer storage.

Furing this temporary storage period, code translation, word-assembly or disassembly, block formation, editing or any otherdata processing that may be required prior to information transfer is performed.

The interface may provide some local automomous control functions in addition to the commands received from the computer. Other facilities desired are to try to correct the corrigible errors before informing the computer, provisions for recovery from the unexpected conditions, minimize the time the computer remains tied up during the data transfer operation and to handle, may be core then one I/O & dovices.

now a days manufacturers not only supply a peripheral device but also a generalised Dévice control system with it, which performs almost all functions stated above except say 1,8, & 4, thus simplifying interfacing.

The functions to be performed by a typical interface in such a situations would be:

- 1. To receive data from the computer and perform data word-disassembly, if required and wansmit to the device control system.

- 2. To receive data from the device control system and perform data word-assembly and transmit to the computer.

- 3. To receive a command word and decode the operation to be performed OR to receive each command on a separate line and communicate to the decice control system the operation required.

It may check out the validity of the command received at that particular moment.

- 4. To receive the device control system status and transmit to the computer on its request.

- 5. To provide means of communicating error conditions which require quick action of the computer.

- 6. Speed difference between the CPU and the peripheral is taken care of either by the device control system, or could be provided by the interface.

# 2-3 Concept of the standard Interface Module.

New concepts are being evolved now a days moving towards standardization of computer interface. Historically computer interface have been built with very little standard-ization. Standardization has following obvious adventages:

- Saving of money and manpower because of non-duplicacy of efforts in interfece design.

- 2. Exitching of peripherals from one computer system to another is simple, e.g. in case a computer system is to be replaced, it is just necessary to plug-in the standard interfaces.

- 3. Easy maintenance of peripherals e.g. a peripheral to be repaired could be plugged out and repaired offline or it could be connected to a small computer (mini or micro) for on-line testing.

schleved by:

- 1. Fixing the physical demensions of interface modules.

- 2. Standardizing paths or buses called data highways or data ways. The connector on back of the modules is plugged into this highway and each wire in the highway is reserved for a specific signal type. The signal characteristics and functions are also specified.

The above concept of computer interfacing may require a very simple interface as a plug on computer cabinet which supplies the appropriate signals to appropriate points of data way or a control module to generate appropriate signals.

# 2-6 Factors affecting on Interface Design.

Design of an interface between an I/O device or a device control system and a computer is affected by a number of factors. The important factors are :

- 1. Modes offate transfer available on the computer.

- 2. I/O structure of the computer.

- 3. I/O device or device control system available.

The maximum data input or output rates with or

without critical timings for data transfer etc.

# 2-4.1 Pata Transfer Techniques.

There are soveral methods for transferring data between a computer and the outside world. These are :

a) Progressed data transfer.

- b) Programmed date transfer with interrupt.

- c) Direct Demory Access transfer.

Interface design for an I/O device is influenced by the data transfer technique to be implemented, the choice of which depends upon the I/O device characteristics (discussed later) to be interfaced with the computer, maximum data transfer rate with which I/O device can communicate, and critical data transfer timings. It may be required to have in an interface for an I/O device, all of data transfer modes. It may be the case that an I/O device provides high data transfer rates but data transfer timings are not critical. Clearly in such a situations, the choice of data transfer mode is also dectated by cost comparisons of different modes of implementation.

In the programmed transfer method, the peripheral is serviced at the convenience of the computer, i.e., when -ever the I/O instructions happen to be reached in the normal programmed sequence. By contrast, the interrupt method places the data transfer at the convenience of the external device, i.e., service is initiated through what moments to on I/O subroutine as soon as the peripheral requests it instead of when the computer gets around to it.

Direct memory access, DMA, is a very quick and officient method for transferring large blocks of information such as when data is passed to or from a disk. It is similar to the interrupt method in that service is initiated immediately, but instead of having a moderate-sized software subroutine supervise the transfer, it is done ontirely by

special hardware. Thus, the data are transferred much quicker at the expense of more complicated and costly hardware.

8-4.8 1/0 Structure of the Computer.

For connecting I/O devices to the computer, there are two systems:

1. BUS SYSTEM: In this system the I/O Dus will have a number of data lines, address lines, and control lines which are shared by the devices. Depending on the address a particular device will be selected and the control signals will activate the device.

Adding a new device, it is just sufficient to have a proper dekice controller which can readily be interfaced with the I/O Bus. The CPU is not required to be madified. The computer has at least one I/O instruction operation code. Typically the op. code, the device number and a few control bits form an I/O instruction.

Thenever CPU interprets on I/O instruction it sends control signals on different control lines of the I/O bus, depending on the control bits of the I/O instruction. If the computer word length is insufficient to accommodate the op-code, the device number and a few control bits, it usually uses one of the working registers, generally accumulators, to hold the device number or the control bits. Any I/O operation to be performed on a given device will require at least two I/O instruction to be executed in this typical order.

- 1. First 1/0 instruction to select the device.

- 2. Second I/O instruction to perform the required operation.

Different combinations of these control bits give rise to different combination of control signals on I/O bus, each of which could be used to perform a specific function.

The interface must have a device selection logic, an instruction decoding logic, and the logic to perform the required function. Complemity of the interface depends on the size of the instruction set chosen to handle the new device and functions to be performed by each instruction in this instruction set.

2. Radial System: In this system, the control signels are different for different devices. So whenever a new device is to be added, the computer CPU is required to be modified.

# 2-4.8 I/O Pevice Characteristics:

Interface design depends on the characteristics of the I/O device to be interfaced or the characteristics of the device controller logic available with it.

The I/O devices are Dinary coded devices or alphanumerican devices. The various I/O devices differ widely in nature. The main characteristics influencing the interface design are:

- 1. Esture of signal available. c.g. analog or digital.

- 2. Pata encoding, decoding and formatting required,

- 3. Speed of the I/O device.

- 4. Critical or non-critical data transfer timings otc.

If the I/O divice has been provided with a device controller logic, then the interface design, depends on the characteristics of the device controller logic, and is usually simplified.

# 2-5 Specification of a computer Interface.

The interface designer should include the following points for specifying the interface developed:

- Detailed information about the device being linked to the computer, alongwith the interfacing requirements on both the sides.

- 2. Command implementation: Instruction set associated with the interface. Specification demands, very clear explanation of each instruction.

- Transfer rates: The user on specifying transfer rates of the interface must also give careful attention to the amount of program manipulation required before the data arrives at the interface and is stored in the computer momory or on the peripheral device, and the effect of presence of the other devices.

- 4. Enintenance and packasing: Maintenance is usually thought of as two activities:

- a) Proventive maintenance Anything from periodic replacement of mechanical components to exercise

- equipment on regular bases.

- details of checkout programs that are envisioned.

Specifications should call out test point that

can be accessed from the front panel or back

panel or any display devices e.g. light emitting

diedes. Specifications should ask for repair

ports list. From repair point of view, interface

should be plug-in type. Finally, specifications

call for packaging details, dimensions, connectors,

front pannel arrangements, logic diagrams etc.

# 2-6 Incremental Flotter interfacing with a computer.

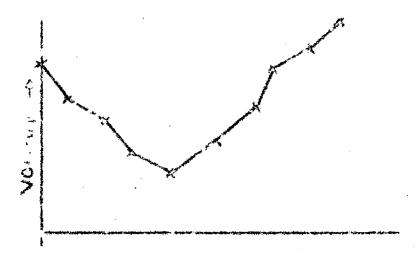

The incremental plotter is an electromagnatic device which accepts degital data on its imput lines and moves the pen past a paper (drum type or flat bed) to produce graphical representation of the data inputs. There are two types of plotter- Drum type and Flat bed type. In drum type plotter paper moves one step at each digital signal bit received on Y-line. It can move in forward direction if signal in comes on + Y line. and it moves backward if the - Y line receives a signal. Pon moves along the length of the drum i.e. at an angle of 90° to the paper covement. Pen can move either to the left or right depending on the signal received either on - X line or + X line respectively. There are two more lines - PEN UP and PEN DOWN which keeps pon up and down respectively.

#### CHAPT'R - 3

# INPUT/QUITPUT GYSTSM OF SC 1020/SOB COMPUTER-MUX CHAMPEL

## 3-1 Organisation of EC 1020 Computer

The general organisation of a typical computer system like EC 1020 can be represented as shown below. The heart of the system is the Central Processing Unit (CPU), shown as comprising of a main storage, which holds both program and data, an arithmatic - logic unit (ALU), which contains processing circuitry such as an adder, shifter, and a few fast registers for holding the operands, and the instruction currently being processed. One part of the CPU is a set of routing circuits which provide paths between storage and the ALU and Input/Output controllers or channels. In this type of system, many storage or Input/Output devices may be wired to one channel, but only one device per channel can be transmitting information from or to main storage at any one time. This is, of course a restriction on the number of devices that can operate concurrently. This is imposed because of the economy of sharing common paths to main storage and simplicity in controlling movement of information between the dovices and storage.

Fig.3.1 General Organisation of a typical digital computer.

The major parts of a computer may be described as follows:

- 1. Storage This is a means for storing a rather large volume of information and a simple economical access mechanism for routing an element of information to/from storage from/to a single point(register). Storage is usually available in several versions, even in the same system (main storage and secondary storage), these very in access time, capacity, and cost.

- 2. Pate Flow The switching networks that provide paths for routing information from one part of the computer to another.

- 3. Transformation The circuits for arithmatic and other data manipulation. This function is usually concentrated in a single Arithmatic logic Unit(ALU). The centralization provides economy since a single set of fast expensive circuits is used in time sequence for all operations. Transformation circuits operate an information obtained from storage by control of the data-flow switching.

- 4. Control This is a general term that includes the important function of performing time sequences of routings of information through the data flow. The control function appears on many levels in a computer. Usually the control is organised

cycle period is commonly (but not always)

divided into equally spaced time units called

intervals. The term "cycle" refers to a specific

type of sequence for selections on the data flow

performed in a succession of clock intervals.

For example, there is an <u>instruction + fetch cycle</u>

during which an instruction containing information

about a transformation is brought from storage to

an ALU register, At each clock interval within

the cycle, an elementary operation is performed

such as routing the storage access mechanism, or

routing of the instruction obtained to an ALU

register.

- 6. Input/Output Since information in the processor and storage of the computer are represented by electric signals, devices are provided to convert information from human-generated to machine-readable

- output. A very common scheme for performing this transducer function uses a punched card. An operator reads the information from hand written or typed documents and enters the information on a key-board of key-puch machine. This machine translates the key strokes into holes on the card. The cards are then sent to the card reader,

the cards, i.e., sense the hole positions and translate them into the internal electric-signal representation. The results of the processing in CPU, can be communicated to the user by means of some other transducer called printer. In the printer, a translation from internal electric signal form to the human readable character set form takes place.

The punched card, printers, and its associated machines are examples of Input/output devices. Other devices available include type writers, puched paper take, CAT displays, analog-digital converters and plotters.

3-2 Input/Output Systems:

Input/Output operations involve the transfer of information to or from main storage and en 1/0 device.

Input/output devices include such equipment as cord-readers and punches, magnatic tape units, disk storage, teletype devices, printers, teleprocessing devices, plotters, and process control equipment.

unit. The control unit function may be housed with the I/O device as in the case of printer, or a separate control unit may be used. In all cases, the control unit function provides the logical and buffering capabilities necessary to operate the associated I/O device. From the programming point of view, most control unit functions marge with I/O device functions.

(

# 3-2.1 Input/output Interface:

All communications between the control unit and the channel takes place over a connection called the I/O interface. The I/O interface provides and an information format and control signal sequences that are independent of the type of control unit and channel and provide a uniform mean of attaching and controlling various types of I/O devices.

### 3-2,2 Chennels:

The channel directs and controls the flow of information between I/O devices and main storage. It relieves the CFU of the task of communicating directly with the devices and permits data processing to proceed concurrently with I/O operations. The channel accepts control informations from the CPU in the format supplied by the programs and changes it into a sequence of signals acceptable to a control unit. After the operation with the davice has been initiated, the channel essembles or disassembles data and synchronizes the transfer of data bytes over the interface with main storage cycles. To accomplish this, the channel maintains and updates an address and a count that describe the destination or source of date in main storage. Then an 1/0 device provides signals that chould be brought to the attention of the supervisor, the channel again converts the signals to a format compatible to that used in CPU.

A channel may be an independent unit, complete with nucessary logical and storage capabilities, or it

Fig.3-2 I/O Interface.

. ( . . .

may share CPU facilities and be physically integrated with the CFU. The channel facilities required for sustaining a single I/O operation are termed as a SUBCHANNEL. The subchannel consists of the channel storage used for recording the addresses count, status and control information associated with the I/O operation. The mode in which a channel can operate depends upon whether it has one or more subchannels. In most of the computer, there are two types of channels.

- 1. SELECTOR CHARREL

- 2. EVLTIPLEXOR CHARMEL

Channels have two modes of operation! BURGE and MULTIPLEX. In the Burst mode, the data transfer facilities of the channel are monopolized for the duration of transfer of a burst of data. Other devices attached to the channel cannot transfer data until the burst ceases. The selector channel fuctions only in the burst mode and so it has only one subchannel.

The multiplemor channel functions in either the burst mode or in the multiplem mode. In the multiplem mode, the multiplemor channel can sustain concurrent I/O operations on several subchannels. Bytes of data associated with different I/O devices are interleaved and routed to or from the desired locations in main storage. The I/O interface is time shared by a number of concurrently operating I/O devices, each of which uses its own subchannels

## 3-2.3 IEPUT/OUTPUT INSTRUCTIONS

I/O operations are initiated and controlled at three lovels by information with three type of formats; INSTRUCTIONS, COMMANDS, and ORDERS. Instructions are decoded and executed by the CPU and are part of the CPU program (first lovel). Commands are decoded and executed by the channels and initiate I/O operations, such as roading and writing (2nd level). Both Instructions and commands are fetched from main storage and are common to all types of I/O units, although the modifier bits in the command code may specify device dependent conditions for the execution of a data transfer operation at the device.

Functions poculior to a device are specified by orders. Orders are decoded and executed by I/O devices. The control information specifying an order may appear in the medifier bits of a control command code, may be transferred to the device as data during a control or write operation, or may be made available to the device by other means.

The CPU controls I/O operations by means of four I/O instructions:

| Melac     |                | Inemonic   | Type | Code       |

|-----------|----------------|------------|------|------------|

| 1. START  | 1/0            | SIQ        | 61,C | 9C         |

| 2. Test I | /0             | 710        | SI,C | 90         |

| 3. HALT I | <b>/</b> 0     | HIO        | SI+C | <b>9</b> E |

| 4. TEST C | HATIU <b>L</b> | <b>PCH</b> | SI,C | of         |

All I/O instructions use the following 81 format:

| Ī |         | 1    |       |       |

|---|---------|------|-------|-------|

| I | OP CODE |      | 91    | 57    |

| 1 |         | 8 15 | 18 19 | 80 31 |

There, Dits 0-7 contains instruction code

Bit 2-15 are ignored

Bit 16-19 Bl field (désignates a bosic register)

Bit 20-31 Dl field(displacement)

The sum obtained by the addition of the content of register Bl and the content of the Dl field identifies the channel and the I/O device. This sum has the format:

|   | Chi   | anne <b>l</b> | Dovice | 1 |

|---|-------|---------------|--------|---|

| , | Adı   | •             | adr.   |   |

| 0 | 15 16 | 24            | 26 3   | ū |

Bit positions 0-15 are ignored.

START I/O (SIO) instruction: This is used to initiate an I/O operation when CPU encounters an SIO instruction, it activetes, the channel and sends the device address to the channel. Channel inturn initiates the device selection sequence which results in the issuing of a command.

On multiplexor channel, SIO causes the addressed device to be selected and the operation to be initiated only after the channel has serviced all outstanding requests for data transfer for previously initiated operations. This instruction is executed only when CPU is executing in the supervisory mode.

# HALT I/Q(HIO) instruction:

HIO instruction terminates a current I/O operation at the addressed sub-channel or channel. The subsequent state of the channel depends on the type of the channel. The instruction HIO is used only then the CPU is executing in the supervisor state.

### TEST CHARMEL (TCH) instruction:

Execution of the TCH instruction sets the condition code in the PSV to indicate the state of the channel addressed by the instruction. The resulting condition code indicates one of the following channel available, interruption condition in channel, channel working, or channel not operational.

# 3-2.4 1/0 operation initiation:

An I/O operation is initiated by a SIO instruction.

If the necessary channel and device facilities are available, and is accepted and the CFU centinues its program. Then after channel independently governs the I/O device specified by the instruction. Successful execution of SIO instruction causes the channel to fetch a CHANNEL APPRESS WORD(CAT) from the main storage location 78. The CAT specifies the byte location in main storage where the channel program begins.

The format of the CAT is shown below. Bits 0-3 specify the storage protection key that will govern the I/O operation. Bits 4-7 must contain zeros. Bits 8-31 specify the location of the first CHARREL COLUMNUT FORD(CCT).

The byte location specified by the CAW is the first of eight byte of information that the channel fetches from the main storage. These 64 bits of information are called channel command word(CCW). Only the SIO instruction may cause the channel to fetch CCW's.

CAW: KEY 0000 Command

o 34 78 Address 31

One or more CCW's make up the channel program that directs channel operation. A channel command word can specify one of six commands:

READ

WRITE

READ BACKWARD

CONTROL

SENSE

TRANSFER IN CHANNEL

If more than one CCW is to be fetched, the CCW's are to be fetched sequentially, except when transfer in channel is encountered. The Figure given below shows the format of the CCW

| Command<br>Code | Data Address |    |

|-----------------|--------------|----|

| 0 7             | 8            | 31 |

| Flag 0000       | ///// Count  |    |

| 32 3637 39      | 40 47 48     | 63 |

The <u>Command code</u> specifies the operations to be performed (Read, Write, Rewind etc.).

The <u>Data Address</u> specifies the first byte location in main storage for a data transfer type of operation.

25

The Flag bits may specify chaining to another CCU. suppression of a possible incorrect length indication otc. The count specifies the number of bytes for a data transfer operation.

### 3-2.5 1/0 Compands:

The command code, bit positions 0-7 of the CCV. specifies to the channel and the I/O unit the operation to be performed. The two low order bits ( or when these bits are 00, the four low order bits) of the command code identify the operation to the channel. The channel distiguishes among the following four operations:

Output forward (write, control)

Input forward (Read, Sense)

Input backword ( Rood backword)

Branching (Transfer in channel)

The channel ignores the high order bits of the command code. Commands that initiate 1/0 operations (Trite, Read, Read backward, Control, and Sense) cause all eight bits of the command code to be transferred to the 1/0 unit. The command code assignment is listed in the following table. The symbol 'X' indicates that the bit position is ignored; E identifies a modifier bit.

| Code        | Command             |

|-------------|---------------------|

| XXXX0000    | Invalid             |

| [IIIIO100   | Sense               |

| 12000 12000 | Fransfer in Channol |

| 17270,000   | Read backward       |

| [227]       | Trite               |

| U:794310    | Read                |

|             | Control             |

The modifier bits specify to the unit how the command is to be executed. They may cause, for example, the unit to compare data received during the Trite operation with data previously recorded, and they may specify such conditions as recording density and pointy. For the control command, the modifier bits may contain the order code specifying the control function to be performed.

The never the channel delects an invalid command during the initiation of a command, the program-check condition is generated when the first CCT designated by the CAT contains an invalid command code, the status portion of the CST with the grogram-check indication is stored during the execution of START I/O.

ERITE: A Trite operation is initiated at the I/O device, and the subchannel is set up to transfer data from main storage to the I/O unit Data in storage are fetched in an ascending order of addresses, starting with the address specified in the CCV. Bit positions 0-6 of the CCV contain modifier bit (mmmmmmol).

BEAD: A head operation is initiated at the I/O unit, and the subchannel is not up to transfer data from the unit to main storage. Data is storage are placed in an ascending order of addresses, starting with the address specified in the CCD.

BYAD BACKTARD: A Read Backward Operation is initiated at the I/O unit, end the subchannel is set up to transfer data from the unit to main storage. The channel places the bytes in storage in a descending order of addresses, starting with the address specified in the CCT, but

fotches CCW's in an ascending sequence.

COUTROL: A control operation is initiated at the I/O unit, and the subchannel is set up to transfer data from the Main storage to the I/O device. The I/O unit interprets the data as control information. The control information is fetched from the main storage in ascending order of addresses, starting with the address specified in the CCU. A control command is used to initiate at the I/O unit an operation not involving transfer of data, such as backspacing or reminding magnetic tape or positioning a disk access mechanisum. For more control functions, the entire operation is specified by the modifier bits in the corrent code, and the cunction is peformed over the I/O interface as an immediate operation.

the sex modifier bits is defined as Ro-operation. The Ro-operation order causes the addressed unit to respond with channel and without causing any action at the unit. Other operations that can be initiated by means of the control command depend on the type of I/O device. Bit positions O-6 of the CCD contain modifier bits.

FERSE: A sense operation is initiated at the I/O unit, and the subchannel is set up to transfer data from the I/O unit to main storage. The data are placed in storage in an ascending order of addresses, starting with the address specified in the CCT.

A control command code containing scrps for

1

Data transferred during a Cense operation provide information concerning both unusual conditions detected in the last operation and the status of the device. The status information provided by the sense command is more detailed then that supplied by the unit status byte and may describe reasons for the unit check condition.

For most I/O unit, the first six bits of the first sense data byte (cense byte O) are common to all I/O units that have this type of information. The six bits are independent of each other and are designated as follows:

| Pite | <u>Designations</u>   |  |  |

|------|-----------------------|--|--|

| 0    | Command Reject        |  |  |

| 1    | Intervention Required |  |  |

| 2    | Eus Out Check         |  |  |

| 8    | ,                     |  |  |

| 4    | Deta chock            |  |  |

| g.   | Очерний               |  |  |

The meaning of the individual bits are self explanatory.

TRAMEPER IN CHANGEL: The next CCV is fetched from the location desinated by the data address field of the CCV specifying transfer-in-channel. This command does not initiate any I/O operation at the channel, and the I/O device is not signaled of the the execution of the command. The purpose of the transfer-in channel command is to provide chaining between CCV's not located in adjacent double word locations in an ascending order of addresses.

## 3-2.6 Input/Output Terminator:

I/O operations terminate with the device and channel signaling end of operation and a request for an I/O interruption.

A command can be rejected during an attempt to execute a START I/O, by such conditions as busy conditions, a channel programming error etc. The condition code set in the Program Status Word (PSW) by an unsuccessful, SIO instruction will indicate one of the following: that a channel status word (CSW) has been stored to detail the conditions that preclude the initiation of the I/O operation, that the equipment is busy, or that the addressed equipment is not operational.

The Channel Status Word (CSW) provides information about the termination of an I/O operation. It can be formed or reformed by start I/O, Test I/O, Halt I/O, or by an I/O interruption. The instruction test channel does not affect CSW. The format of the CSW is as shown below:

| Key | 0000  | Command A | ddress |

|-----|-------|-----------|--------|

| 0 3 | 4 7   | 8         | 31     |

| (   | Stati | rs Co     | ouni   |

| 32  |       | 47 48     | 63     |

Key field contains the protection key used in the last operation.

Command Address: specifies the (location +8) of the last CCW used.

Status field contains a unit status byte and a channel

status byte. The unit status byte may indicate one or more conditions- such as control unit end, channel ond, Davice end, attention, busy, status modifier, unit check and unit exception. The channel status byte may indicate a channel programming error, a channel data check, a channel control check, protection check, interface control check, chaining check, program controlled interruption, incorrect length, Count field specifies the residual count of the last CCT used.

## 3-8.7 I/O Interruption:

I/O interruptions are caused by termination of an I/O operation or by operator intervention at the I/O device. An I/O interruption stores the current PSV in the I/O old PSV location, and places the I/O new PSV in control of the system. The I/O new PSV, when made current by an I/O interruption, may cause CPU interrogation of the channel status word, or take whatever action is considered appropriate by the programmer.

An I/O interruption request may be intiated by an I/O interruption condition in a device, a control unit, or a channel. When a channel has multiple I/O interruption requests pending it establishes a priority sequence for them before initiating an I/O interruption request to the CPU conditions responsible for I/O interruption was request remain pending in the I/O devices or channels until they are accepted by the CPU.

## 3-2.8 PARIC PROCEDURE FOR A DATA TRANSPER OPERATION

A START I/O instruction is used to initiate data transfer to or from an I/O device. To perform such an operation, it is necessary for the programmer to:

- 1. Establish a channel commond word (CCV) or a list of CCV's in main storage.

- 2. Load the channel address word(CAV) with the address of the first byte of the first CCV in the channel program.

- 3. Load the channel and device address in the START I/O instruction to be used for the operation.

- 4. Fot the system mask to disable all channels for I/O interruptions.

- 5. Issue the START I/O instruction.

- 6. Test the condition code established in the current PET by termination of the START 1/0.

Condition code O indicates that the I/O operation has been initiated and that the channel is proceeding with its execution. If an I/O interruption is desired upon termination of the operations, the pertinent channel mask bit must be set to 1( an appropriate I/O new PSC must have been established previously).

Condition code 1 indicates that a channel status word (CEU) hasé been stored; its status bytes should be examined to determine thy the desired operation was not initiated.

Condition code 2 indicates that the channel or subchannel addressed by the START I/O instruction was found to be busy with a previously initiated operation. If an

I/O interruption from the operation already in progress is desired, the channel mask bit must be set to one.

Condition code 3 indicates that the addressed equipment is not operational; a message to the operator may be initiated.

Between the time a START I/O instruction is decoded by the CPU, and the time the CPU is released by the channel with condition code O set in the current PSW, the channel performs many functions. The CAW must be fetched, the first CCW must be fetched, the CAW and CCW must be tested for validity, etc. After a START I/O results in condition code O, the operation continues until terminated. Termination of an I/O operation causes a request for an I/O interruption.

#### 3-3 MULTIPLEXOR CHANNEL:

# 3-3.1 BASIC DATA PATHS AND BLOCK DIAGRAMS

General block diagram of the CPU and I/O channels is given in Fig 3.3. The channel and the CE panel are connected to the CPU by the block of channel control (BCC). BCC consists of assembly logic and some other schemes (for example, register for channel control-RCC) which will be discussed later.

Fig.3-3 General Block diagram of the CPU & I/O System.

## 3-3.2 HICROPHOGRAM CONTROL OF THE I/O EXETEMS

The data and control information transfer between the channels and the external devices is realized by microprograms and control circuits. Microprogram control is applied for all channels. In the selector channels, a special control Ckt. is used for data transfer. The I/O microprograms are located in the 1st block of ROM and use control signals from the microprogram block of the CPU.

3-3.3 MULTIPLEXBR CHAUMEL BLOCK DIAGRAM AND DATA FLOT:

EC 1020 multiplexor channel (EC) coordinates and controls the work of a great number of small rate I/O devices: the maximum transfer rate in multiplex mode is 14-26 Kbytes/sec.and in burst mode this rate is upto 200 Kbytes/sec.

in Pig.3.4. The multiplexor channel has a comparatively small own hardware because during the execution of channel operation it shares the hardware of the CPU and so a computing process at the same time cannot be realized. The multiplexor channel uses the multiplexor and the local storage. In the multiplexor, which is a part of the main storage, the subchannels are situated. In the subchannels the UCU (unit control words) are stored. The local storage is a complementary hardware in the execution of the channel microprograms.

In the multiplexor channel, the control and the data transfer are realized partly hardware and partly microprogram. The own hardware of the multiplexor channel includes several registers and control schemes.

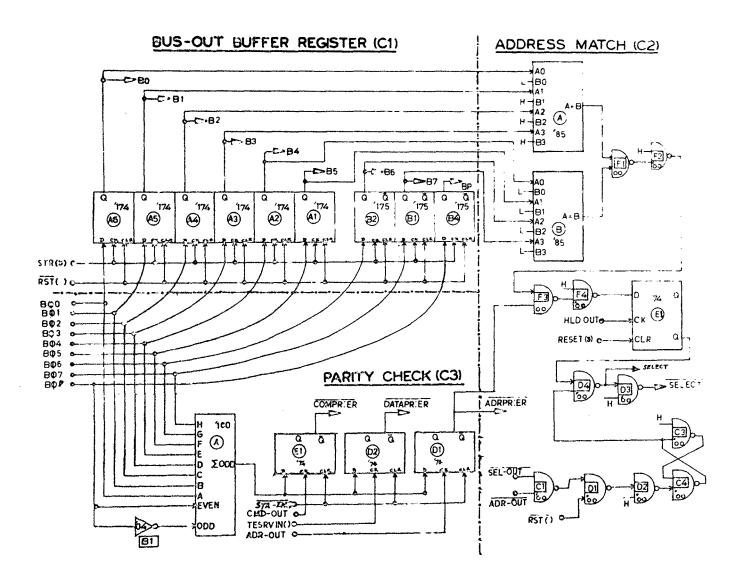

- register of output information RRS, which controls the BUG-OUT interface lines. This register consists of 8 informational bits and of one parity bit. The functional schemes of the register RRS and other multiplexor channel registers are described in paragraph S.4.

- register of input information RR3. This register is connected with the BUS-IN interface lines and 8 informational bits and one paints parity bit.

- control register for in-bound interface lines

RR4, connected with the in-bound tag and control

lines. The register has the following bits:

## <u> 194</u>

| ō | ***       | (TPC)      | Interfa    | e froe c  | ondition.      |            |

|---|-----------|------------|------------|-----------|----------------|------------|

| 1 | -         | (TOPL-111) | Trigger    | for the   | interface sign | nel OPL-IN |

| 2 | *         | (TADR-IN)  | Triegor    | for the   | interface sign | 201 ADR-IN |

| 3 | *         | (TSTe-IN)  | ę;         | ₹1        | •              | STA-IN     |

| 4 | *         | (Terv-IH)  | et .       | n         | Ħ              | erv-In     |

| 6 | #         | (TEEL-IU)  | 11         | 17        | n              | CEL+III    |

| 8 | <b>**</b> | (11-g-17)  | <b>f</b> 5 | te        | n              | RE3-IN     |

| 7 | •         | (Trel U)   | Trigger    | for contr | ol unit selec  | tion. This |

|   |           |            | shows th   | at solect | tion is initia | ted by the |

|   |           |            | channel.   | ı         |                |            |

- register for output channel control RRC, which is connected with out-bound interface tag and control lines. The register consists of the

...

#### following bite:

#### DPA

| 40 | -  |           |     | -        |         | -         | -      | فلساب يتدسست نبده |

|----|----|-----------|-----|----------|---------|-----------|--------|-------------------|

| 0  |    | (TCEL-OUT | ec) | Trigger  | for the | interface | signal | SEL-OUT           |

| 1  | -  | (TADR-OUT | EC) | įs.      | **      | n         |        | ADR-OUT           |

| 8  | •  | (TCID-OUT | EC) | ts.      | ti      | 10)       |        | CLD-OUT           |

| 3  | *  | (TBRV-OUT | EC) | <b>P</b> | ##      | n         |        | GRV-OUT           |

| 4  | ** | (TOPL-OUT | EC) | n        | . 44    | e         |        | OPL-OUT           |

| 5  | *  | (THUP-OUT | EC) | \$.      | *1      | ø         |        | SUP-OUT           |

| 6  | -  | (TSEL-OUT | EC) | **       | #1      | • 61      |        | SEL-OUT           |

| 7  | *  | (TCDEC)   |     | trigger  | for cha | in deta   | •      |                   |

|    |    |           |     |          |         |           |        |                   |

error register RRE. This register fixes the error situations during the operations of the sultiplexor channel and has the following bits:

## MER

0 - (TEISCEC) trigger for multiple interface signals check

<sup>1 - (</sup>TISCUC ) trigger for interface signals check

<sup>2 - (</sup>TIPCEC ) trigger for interface parity check

<sup>3 - (</sup>TOCCMC ) trigger for output ALU lines C check

<sup>4 - (</sup>TCDECC ) trigger for channel data check

<sup>5 - (</sup>PCCCMC ) potential channel control check

<sup>6 - (</sup>PICCEC ) potential interface operation check

error register RRE. This register indicates

an invalied response, slow response or no

# response from I/O device to a tag-out interface signal and has the following bits:

#### BRE

| o - (TLISEL - OUTLE)  | first trigger for interface operation  |

|-----------------------|----------------------------------------|

|                       | interrupt ofter the signal STLOUT      |

| 1 - (TRISEL - OUTEC)  | socond trigger for interface operation |

|                       | interrupt after the signal SFLOUP      |

| 8 - (MISAV - OUTEC)   | first trigger for interface operation  |

|                       | interrupt after the signal CRV-OUT     |

| 3 - (Teisry - Outlic) | second trigger for interface operation |

|                       | interrupt after the signal SRV-OUT     |

| 4 - (TICLD - OUTEC)   | first trigger for intorfoce operation  |

|                       | interrupt efter the signal CLD=OUT     |

| 8 - (TRICED - OUTEC)  | second trigger for interface operation |

|                       | interrupt efter the signal CLD-OUT     |

| 6 - (TIOPL - ICEC )   | Triggor for interface operation        |

|                       | interrupt after the signal OPL-ID      |

| 7 - ( PIOIEC )        | Trigger for interface operation        |

|                       | interrupt.                             |

|                       |                                        |

The channel hardware also includes some control schemes:

- Scheme for forcing ROS interrupt (ROSI) signal,

- Echeme for forming REB (reset U/C errors) signal etc.

The data branefer between the cain storage and the control unit is done via the input information register

RRS and output information register RR2, connected with the register NZ of the main storage. The data transfer to the register RR2 and from the RR3 is microprogram controlled.

The input of the register RR2 is also connected by the assembly schemes in the BCC to the output C of the ALU and for that reason the output of the RR3 is connected by the assembly logic in the BCC to ALU-B input.

The transfer of control signals to the corresponding interface lines from the channel is from the register RRG. Dome triggers of this register are set as bits of RRL register. For analysing the contents of the RRG register, its output is connected to the input \*B\* of the ALU.

The interface signals from the external device are transferred for analysis via register RR4 to the input "B" of the ALU. The error registers RRB and RRB are also connected to the input "B" of the ALU and their contents can be analysed by the miscroprogram.

all registers in the mext mux channel are connected either to input "D" or to output "C" of the ALU. This connection requires the maximum no of register bits to be eight without a parity bit.

# 3-3.4 HARDWARE OF THE MIK CHATTEL

The nux channel hardware can be devided into three main groups:

1. The first group includes all schemes for maintaining the standard interface dialogue.

. 1

Registers ARC and RR4 and some control triggers belong to this group.

- 2. The second group includes registers for servicing the data flow from the main storage to external devices and vice versa. Registers RR2 and RR3 belong to this group.

- 3. Registers RRE and RRE are in the third group and serve for checking and handling errors in channel operations.

## 3-4 General 1/0 Interface Fequence - Eultiplexor Channel

The I/O interface provides an information format and a signal # sequence common to all I/O units. The interface consists of a set of lines that can connect a number of control units to the channel. Except for the signal used to establish priority among control units, all communications to and from the channel occur over a common bus, and signal provided by the channel is available to all control units.

Control unit is a piece of hardware that provides the logical capabilities necessary to operate and control an I/O device and adapts the characteristics of each device to the standard form of control provided by the channel. The control units accept control signals from the channel, controls the timing of data transfer over the I/O interface, and provides indications concerning the status of the device.

The I/O interface (channel to control unit) is the communication link between the CPU channel and the various

I/O control units in the EC 1020 system. It employes information formats and control signals sequencing to provide inform means for attaching and controlling various type of control units.

This interface is so designed that it provides:

- a degree of consistency of I/O programming over

a wide range of control units.

- ready physical connection to EC 1020 system channels of control units designed by any manufacturer to operate with this interface.

- ability to physically accompdate future control units designed to meet the parameters of this interface.

- en interlocked interface operations that is not

very time dependent, this feature increases

the range of control units that may be attached.

- an operation applicable to both multiplex and burst code operations as well as many control operations and channel-to-channel transmissions:

- upto eight control units serviced por set of lines.

At any one time, only one control unit can be logically connected to the channel. A control unit remains logically connected to the interface until it transfers the information it needs or has, or until the channel signals of it to disconnect.

The rise end fall of all signals transmitted over the interface are controlled by interlocked responses.

. (

Interlocking removes the dependence of the interface on ckt. speed, and makes it applicable to a wide variety of ckts. and data rates. Further, interlocking permits connecting control units of different ckt. speeds to a single channel.

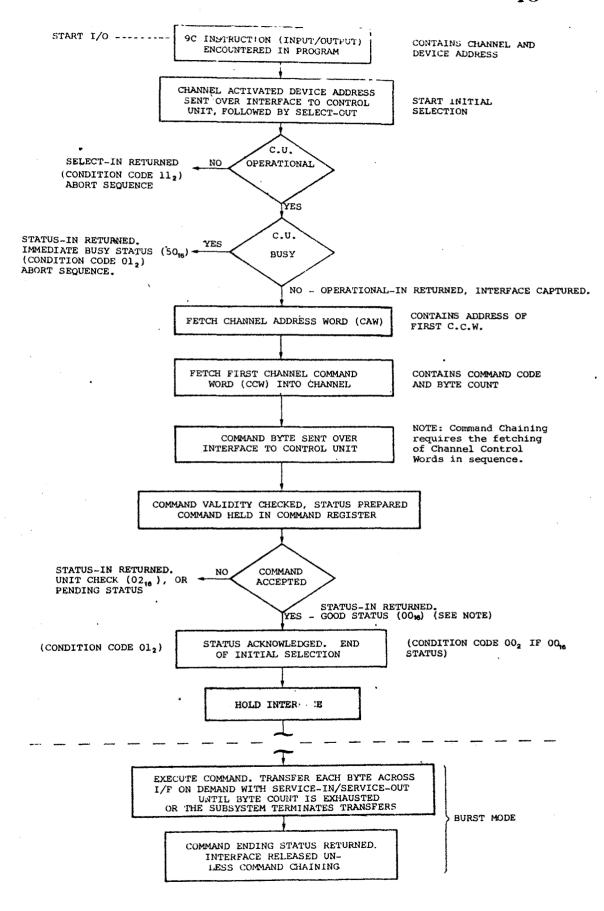

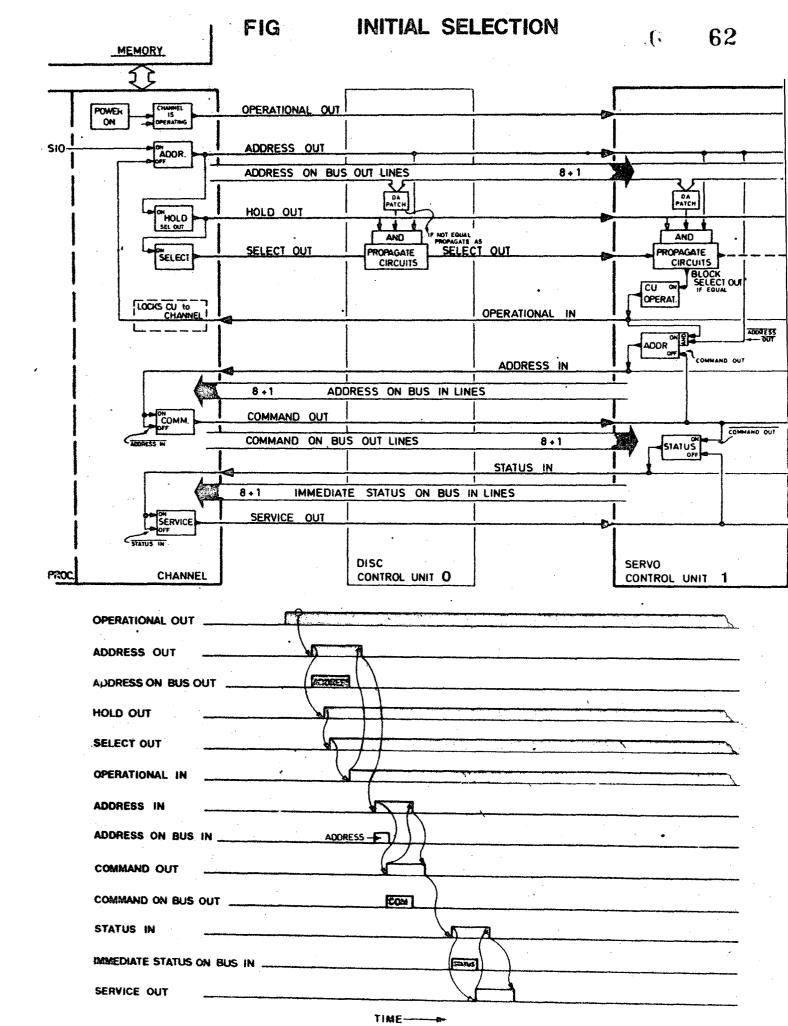

The I/O activity commences with the START I/O instruction (96) which is encountered in the program. It indicates the channel address together with the address of the device which is to be used. This device address represents the chosen peripheral device (Endule), as well as the control unit through which it operates. The device address is placed on the bus-out to all connected control units and by means of patch-cards, the chosen one is identified.

condition of its readness, must be reported to the processor.

This is achieved by the status byte, which is prepared in the control unit and sent to the channel, and by the two bit condition code, which is prepared in the channel and sent to the processon. The flow chart shows the various situations and the status or conditions which can be reported.

have been previously prepared and reside in memory. These words namely CAT and CCT, are used to provide the control of all activity with the current selected device. The CAT points to the first CCT which when fotched into the channel, provides the necessary controlling parameters. It contains the command code, as per the device instructional repertoire, with certain flag bits, which indicate special operations.

The flag bits may specify, for example, whether the command is self standing or is issued as a part of a claim of commands. The CCV also contains the address where the data is to be located in memory or where data is to be placed during the current transactions. The smount of data bytes which have to be transferred with the current command is also specified in the CCV i.e. the byte Count. The CCV is fatched into the channel and is executed in order to initiate operation. It continually updates this countain as each byte transfer takes place. It is therefore maintained within the channel, always to reflect the current situation.

prior to the start of any data transfer, the command byte, extracted from the CCT, must be delivered to the control unit and checked for validity, relative to the addressed module. If the command is invalied, the status of unit check(O216) is returned. Alternatively, any status condition which may exist (pending) for the selected module is reported by means of the status byte at this time. If the command is accepted, the status returned depends upon the type of command which was issued. Certain command not involving a data transfer, may be executed almost incediately. Therefore, the status byte returned at this time may contain command - ending status. If the command involves a data transfer, a zero status will be returned which indicates an acceptance to proceed into the execution phase.

The acknowledgement of status by the channel signifies the end of the Initial-selection phase and since data is to be transferred in the burst mode of operation,

the interface with the selected device is held until the completion of the data transfer.

#### CHAPTER - 4

#### EXCLUSIVE CONTOURNING DESCRIPTION

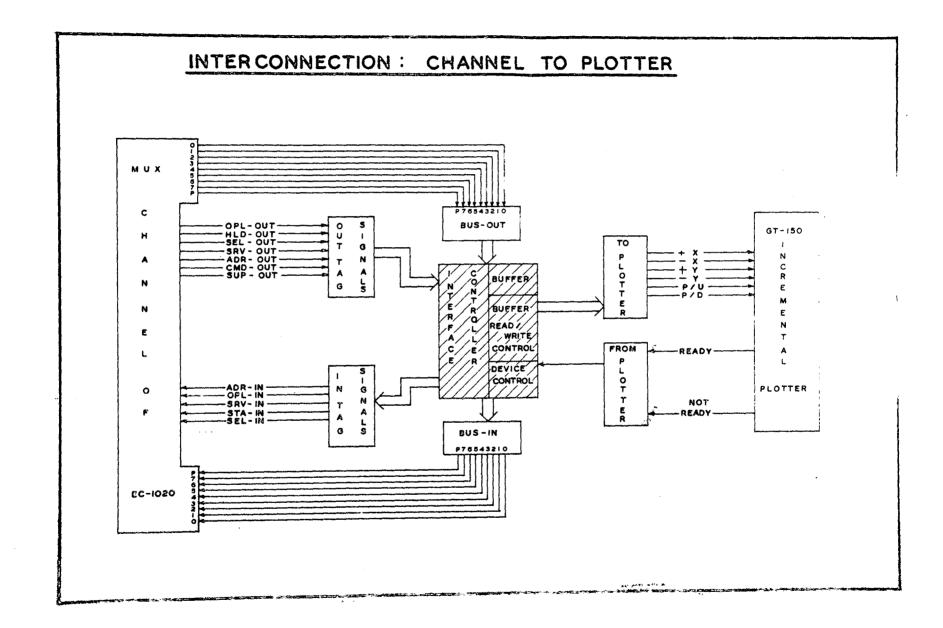

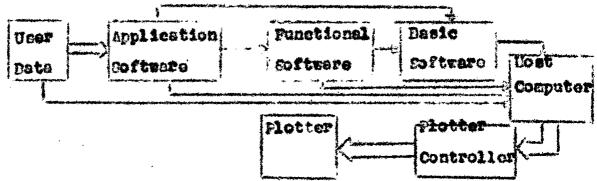

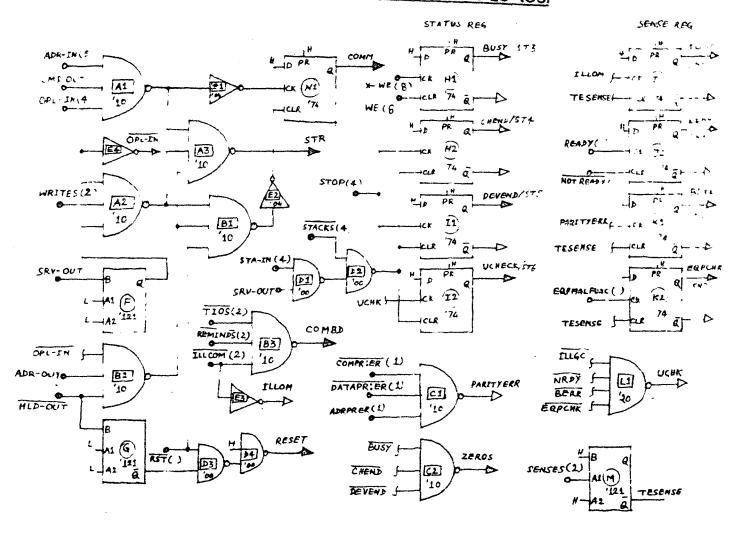

4-1 Evatem Block Diagram: The complete system of 1/0 interfacing can be divided into three portions: Channel portion, controller portion and device portion, Channel provides the standard set of lines (signals) to the controller. These lines can be grouped in the following general way:

Information lines

- DUS-IN and BUS-OUT

used to transfer an eight bit

byte plus one parity bit, in

parallel.

Control or Tag lines

- ADDRESS-IN and ADDRESS-OUT

SERVICE-IN and SERVICE-OUT

STATUS-IN

COMMAND-OUT

Used to define the contents of the Dus-lines which, at different tenacs, can carry any of the following:

The Device Address

The Command

Data

Status (In only)

Coloction and Priority

Lines

- SELECT-OUT and SILECT-III

HOLD-OUT

mequeer-in

OPERATIONAL-OUT OPERATIONAL-IN

Different combinations of these signals convey different massage to the controller. The main function of the controller is to understand these massages and act accordingly. All the signals, except data on the BUS-OUT, are meant for controller. Controller accepts data from the channel and sends it to device in a format acceptable to it. Thus data formatting is done by the controller.

of them Input and others output. It is operated by these input lines and informs its status to the controller with the help of output lines. The system block diagram is shown in Figure 4.1. There are six input lines two output lines in this device. The input lines are: +x, -x, +y, -y, pen up and pen down. The two output lines afe: Ready and not ready.

# 4-2 1/0 Interface Structure and Signal Sequences:

The I/O interface(channel to control unit) is the communication link between the CPU channel and the various I/O control units in EC 1020 system. The following are the important features of this standard interface:

- Ability to physically accommodate future control units designed to meet the parameters of this interface;

- 11) An interlocked interface operation that is not very time-dependent; this feature increases the range of control units that may be attached;

- iii)An operation applicable to both multiplox and burst mode operation as well as many control operations and channel to channel transmissions.

iv) Upto eight control units serviced per set of lines.

Informations in the form of data, status and sense information, control signals, and device addresses, are transmitted over the time and function shared lines of interface. These 34 lines are shown in the figure 4.2.

| YOUGHT GCA*        | inese of lines are snown in tha | rrgure 4.8.      |

|--------------------|---------------------------------|------------------|

| 411111             |                                 | 71111            |

| M //               | (8+1)Lines DUG-OUT              | Device           |

|                    |                                 | - 1 ON           |

|                    | (8+1) Licas RUT-III             |                  |

|                    | 3 Lines PAGE-OUT                | -// Unit         |

|                    | 3 Lines Tost-III                |                  |

|                    | 7 Lines SEL CTION CONTROLS      |                  |

|                    | 2 Lines E TENIE CONTROLO        | _}/ <sub>/</sub> |

| 11111/2<br>11111/2 |                                 | 1/1/////         |

Pig. 4.2

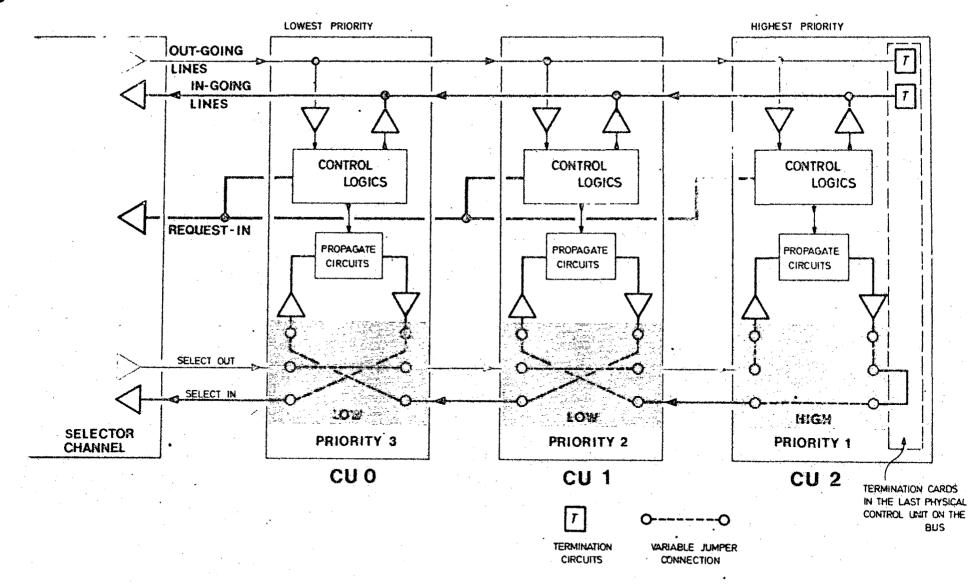

Except for signals used to catablish selection control, all communications to and from the channel occur over a common bus; i.e. any signal provided by the channel is available to all control units. At any one time,

however, only one control unit can be logically connected to the channel. Selection of a control unit for communication with the channel is controlled by a signal (pansing serially through all CUE) that permits sequentially, each control unit to respond to the signal provided by the channel. A control unit remains logically connected to the interface until it transfers the information it need or has, or unfill channel signals it to disconnect.

The rise and fall of all signals transmitted over the interface are controlled by interlocked responses. Interlocking removes the dependence of the interface on cht. speed, and cakes it applicable to a wide variety of circuits and data rates. Further, interlocking permits connecting control units of different cht speeds to a single channel.

The I/O interface lines are grouped in the following way:

BUS-OUT

- used to transmit information (data, device address, commands, control orders) from channel to the control unit.

BUD-IN

used to transmit information (data, selected device identification, status information, sense data)

from device control unit to the channel.

TAGS-OUT

- used for identifying the type of information on the BUS-OUT (data, address, command, or control

information). They are: ADR-OUT, CLEB-OUT, SRV-OUT.

TAGC-IN

- used for identifying the type of information on the BUS-IN (date, dovice identification, status, sense byte). They are: ADR-IN, STA-IN, SRV-IN.

SELECTION CONTROLS

- used for the scanning of, or tho selection of, attached I/O units.

They are: OFL-OUT, OPL-IN, BLD-OUT, SEL-OUT, SEL-IN, SUP-OUT, REQ-IN,

METERING CONTROLS

- used for the conditioning of usage meter located in the various attached units.

## 4-2.1 LINE PUPINATION:

eight information lines and one parity line. Information on the buses is arranged so that bit position 7 of a bus always carries the low order bit within an eight-bit byte. The highest order bit is in position 0 and intervening bits are in descending order form position 1 to position 6.

4-2.1.1 TAGS-OUT: It consists of three lines

ADREES-OUT(Adr-out) - This is a tag line from the channel to all attached control units. It provides two functions.

1. I/O device selection - Adr-out is used to signal all the control units to decode the I/O device address on DUS-OUT. The CU when recognises the address, must respond by raising its Opl-In line when its, incoming set-out rises with

address out still up. The rise of Adv-out precedes the rise of set-out by a minimum of 400 ms and follows the placing of the 1/0 unit address on Bus-Out by at least 250ns.

2. <u>Disconnect Operation</u> - It Hid-out is down and Adv-out rises or Adr-out is up and Hid-out falls, the presently connected CU must drop its Opl-In, thus disconnecting form the interface.

co. HAND-OUT(Cmd-Out) - This is a tag line from channel to all attached I/O devices used to define the content on the Bus-Out. The presence of this signal on the interface conveys different meaning in different situations. In the case of channel initiated sequence, the wise of this signal indicates that the content of the Bus-out is a command byte. Untile in the case of device initiated sequency, the rise of Cmd-out signal does not define the content of the Bus-out but simply indicates to 'Proceed' further.

SERVICE-OUT(Grv-Out) - This is also meant for defining the content of the Bus-out. Then Srv-out rises in response to Srv-In during the execution of a write or control chamand, the nature of the information on But-out depends on the type of operation. For example, during a write operation it contains data to be recorded by the I/O device. During a control

operation, it can specify an order code or a second-level address within the control unit or I/O device.

## 4-2.1.8 <u>TAGG-IH</u>:

ADDRES-IN(Adr-In) - is used to signal the channel when the addresses of the currently selected I/O device has been placed on the Dus-In. The channel responds to Adr-In by Cmd-Out. The rise of Adr-In indicates that the address of the currently addressed I/O device is available on Bus-In. Adr-In must fell so that Cmd-Out may fall. Adr-In cannot be up concurrently with any other inbound Tag line.

CTATUS-IN (Sta-In) - is used to signal the channel when the device has placed status information on the Dus-In. The channel responds with either Srv-Out or Cmd-Out depending on whether it accepted the status byte or not.

Channel when the selected I/O device wents to transmit or receive a byte of information. The nature of information associated with Erv-In depends on the operations and the I/O unit. During Road, Read Backward, and sense operations, Erv-In rises then information is available on Bus-In.

During write and control operations, Erv-In rises

when information is required on the Bus-Out. It cannot be up concurrently with any other inbound Tag line.

## 4-2.1.3 GELECTION-CONTROL:

These lines control the selection of the device and require further description, as follows: SELECT-OUT (Sel-Out) - The signal is generated in the channel and sent to the control unit placed physically first in line. The action within the control unit. on receipt of this signal, depends upon the configuration of its wired priority patchcard. Two configurations are possible mamely high or low priority. The propagation of this signal is discussed in section 4-2.2. HOLD-OUT(Hid-Out) - This signal generated in the channel, allows the gating of Sel-Out within the control units. Without Hld-Out, Sel-Out wouldn't function correctly. Hid-Out is used to obtain a more rapid response on disconnect than could be obtained by dropping Sel-Out. The reason for this is that the trailing edge of Sel-Out would take time to be propagated to the connected control unit. SUPRESE-OUT(Sup-Out) - This signal, gonerated in the channel peforms several functions, for example: it can be used to suppress data or status and to suppress Req-In, from a device requiring connection for the transference of a status or data byte.

Sup-Out also indicates command-chaining, allowing a resolection esquence to take place for the purpose of delivering a further command to the same device. Similar activity occurs in the command retry sequence. Finally. Eup-Out also enables a selective reset sequence if present when Opl-Out is inactive. OPERATIONAL OUR (Opi + Out) - This line acts as an interlock for all lines originating at the channel. Except for Sup-Out all lines from the channel are eignificant only when Opl-Out is active. It indicator that the interface area of the channel is ready. The deactivation of Opl-Out, in conjunction with the absence of Sup-Out, indicates a System Reset action. De-activating Opl-Out during the presence of Sup-Out, indicates a Selective Reset to a currently operating device i.e. one where Opl-In is active. Thenever Opl-Out is dropped, any operation in progress over the interface will cease. OPERATIONAL-IN( Opi-In) - This line when activated by the selected device, indicates that it is operational and reedy to accept a carrand. This is o positive response by the device to the Sel-Out signal generated in the channel. With this response the interface is captured for the selected device and the sequence can continue. This is true for all I/O activity whether the selection sequence is initiated by the channel or the device. REQUEAT-IF (Reg-In) - indicates that the control

unit is ready to present status information or date and thus is requesting a selection sequence. Req-III should be dropped when Opl-In rises, unless additional selection sequences are required, or when the control unit is no longer ready to present, the status information or data. Req-In must in no case fall later than 250ns after the fall of Opl-In, if the sequence satisfies the service requirements of the control unit.

SFLECT-IN (Sel-In) - is a line that extends the Sel-Out signal from the jumper in the terminator block to the channel. It provides return path for the sel-out signal.

+6V D.C. SUPPLY - This voltage level on the interface is used to enable a certain part of the interface logic within the connected devices. Thus, effectively, the interface areas in the devices, whilest physically remote from the channel are electrically part of it. This enables certain interface activities to take place independently from the power supply condition of the central unit. For example Sel-Out can still be propagated from a non-operational control-unit.

# 4-2.1.4 PUS-OUT:

It consists of g lines (8 infromation lines and 1 parity line). Thus on this bus at one time one byte wide information can be transmitted from channel to device control unit. At different times, different type of information can be transmitted on this bus such as data byte. I/O address, commands and control

orders. The nature of the information byte presented over Bus-Out can be determined with the belp of Tags-Out signal present and the sequence of events occured.